| Министерство образования Российской Федерации

Институт переподготовки кадров

Уральского государственного технического

университета

Кафедра микропроцессорной техники

Курсовой проект

ТЕМА: Канал последовательной связи на основе МС 8251

Пояснительная записка

Руководитель доц., к.т.н. И.Е. Мясников

Слушатель гр. СП-923 А.С.

2001г.

Содержание

1. Введение (постановка задачи)

2. Состав контроллера последовательного интерфейса

· Регистр буфера передатчика (

THR

).

· Регистр буфера приёмки (

RBR

).

· Регистр буфера младшего байта делителя (

Divisor

Latch

LSB

).

· Регистр буфера старшего байта делителя (

Divisor

Latch

MSB

).

· Регистр разрешения прерываний (

IER

).

· Регистр идентификации прерывания (

IIR

).

· Регистр управления линией (

LCR

).

· Регистр управления модемом (

MCR

).

· Не используемый регистр (

Scratch

Register

).

3.Последовательная передача данных

4. Протокол последовательной связи.

5. Общие сведения о интерфейсе RS–232С

6. Таблица 1.5 Функции сигнальных линий интерфейса RS–232C.

7. Таблица 1.6 Основные линии интерфейса RS–232C.

8. Виды сигналов

9. Усовершенствования

10. Тестирование канала RS–232C

11. Использованная литература

Введение

Контроллер последовательного интерфейса предназначен для обеспечения связи по протоколу

RS232C.

В настоящее время известны и другие реализации этого контроллера, как совместимые с рассматриваемым адаптером, так и не совместимые.

Реализация контроллера RS-232C выполнена на основе МС 8251.

Следует отметить, что основное внимание уделялось основным принципам управления самого контроллера и практически не рассматривались вопросы взаимодействия с модемом и другим периферийным оборудованием использующим этот контроллер.

Постановка задачи

Составить структурную схему RS-232C; описать состав контроллера последовательного интерфейса и протокол последовательной связи, устройства для тестирования RS-232C.

Состав контроллера

последовательного интерфейса.

В состав контроллера последовательного интерфейса входят следующие регистры:

· Регистры буферов приёмника и передатчика,

· Регистры разрешения и идентификации прерываний,

· Регистры управления и состояния линии,

· Регистры управления и состояния модема,

· Регистры буфера делителя генератора.

В таблице 1.1 приведены адреса всех программно доступных регистров. Адреса в этой таблице даны относительно базового адреса контроллера[1]

.

Реклама

Таблица 1.1

| Адрес

|

Операция

|

Регистр

|

DLAB

|

| 0

|

W

|

Буфер передатчика(THR)

|

0

|

| 0

|

R

|

Буфер приёмника (RBR)

|

0

|

| 0

|

R\W

|

Младший байт буфера делителя (Division Latch MSB)

|

1

|

| 1

|

R\W

|

Старший байт буфера делителя (Division Latch MSB)

|

1

|

| 1

|

R\W

|

Регистр разрешения прерывания (IER)

|

0

|

| 2

|

R

|

Регистр идентификации прерывания(IIR)

|

X

|

| 3

|

R\W

|

Регистр управления линией (LCR)

|

X

|

| 4

|

R\W

|

Регистр управления модемом (MCR)

|

X

|

| 5

|

R

|

Регистр состояния линии (LSR)

|

X

|

| 6

|

R

|

Регистр состояния модема (MSR)

|

X

|

| 7

|

R\W

|

Неиспользуемый регистр (Scratch Register)

|

X

|

Базовый адрес контроллера в зависимости от номера контроллера располагается в сегменте данных BIOS и приведён в таблице 1.2

Таблица 1.2

| Номер контроллера

|

Адрес в сегменте BIOS

|

Номер прерывания

|

| COM1

|

0040:0000

|

IRQ4 (INT 0Ch)

|

| COM2

|

0040:0002

|

IRQ3 (INT 0Bh)

|

| COM3

|

0040:0004

|

Не фиксирован

|

| COM4

|

0040:0006

|

Не фиксирован

|

Таблица 1.2 содержит адреса полей в области данных BIOS, в которых расположены базовые адреса контроллеров последовательного интерфейса. Базовые адреса контроллеров заносятся в сегмент данных BIOS программой POST (Power On Self Testing) при проверке после включения электропитания. Программа POST помещает базовые адреса контроллеров последовательно один за другим. Это означает, что между значащими полями не может быть нулевого поля.

Рассмотрим подробно назначение и содержимое регистров контроллера последовательного интерфейса.

Регистр буфера передатчика (

THR

).

Имеет адрес 0 относительно базового адреса контроллера. Данный регистр доступен только по записи и при значении бита разрешения доступа к делителю (DLAB) в регистре управления линией (LCR), равном 0. Регистр THR содержит восемь битов данных (бит 0 является младшим значащим разрядом и посылается первым в канал передачи).

Регистр буфера приёмки (

RBR

).

Имеет адрес 0 относительно базового адреса контроллера. Этот регистр доступен по чтению(IN) и при значении бита разрешения доступа к делителю(DLAB) в регистре управления линией (LCR),равном 0. Регистр RBR содержит восемь битов данных (бит 0 является младшим значащим разрядом и принимается первым из канал передачи).

Регистр буфера младшего байта делителя (

Divisor

Latch

LSB).

Регистр имеет адрес 0 относительно базового адреса контроллера. Этот регистр доступен по чтению и записи только при значении бита разрешения доступа к делителю (DLAB) в регистре управления линией (LCR), равном 1. При записи в этот регистр нового значения делитель перезагружается немедленно.

Реклама

Регистр буфера старшего байта делителя (

Divisor

Latch

MSB).

Регистр имеет адрес 1 относительно базового адреса контроллера. Этот регистр доступен по чтению и записи только при значении бита разрешения доступа к делителю (DLAB) в регистре управления линией (LCR), равном 1. При записи в этот регистр нового значения делитель перезагружается сразу.

Регистр разрешения прерываний (

IER).

Имеет адрес 1 относительно базового адреса контроллера. Этот регистр доступен по чтению и записи, но только при значении бита разрешения доступа к делителю (DLAB) в регистре управления линией (LCR), равном 0. Этот регистр позволяет управлять четырьмя типами прерываний, порождаемыми контроллером последовательного интерфейса. Формат регистра приведён ниже.

| 7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| 0

|

0

|

0

|

0

|

ICM

|

ICL

|

IFB

|

IDA

|

ICM задаёт прерывание при изменении состояния модем:

1 – прерывание вырабатывается;

0 – прерывание запрещено;

ICL определяет прерывание при изменении состояния линии приёмника:

1 – прерывание вырабатывается;

0 – прерывание запрещено;

IFB задаст прерывание при освобождении регистра буфера принимаемых данных:

1 – прерывание вырабатывается;

0 – прерывание запрещено;

IDA определяет прерывание при доступности принимаемых данных:

1 – прерывание вырабатывается;

0 – прерывание запрещено;

Биты 7-4 не используются и должны принимать значение 0.

Регистр идентификации прерывания (

IIR).

Регистр имеет адрес 2 относительно базового адреса контроллера. Этот регистр доступен только по чтению и позволяет получить информацию от контроллера о ждущем прерывании. Значение битов регистра приведено ниже.

| 7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| 0

|

0

|

0

|

0

|

0

|

I Type

|

II

|

Биты I Type определяют тип ждущего прерывания, если оно хранится контроллером (что определяется битом II):

11 – изменилось состояние линии приёмника;

10 – принимаемые данные доступны;

01 – освобождён регистр буфера;

00 – изменилось состояние модема.

Более подробная информация о приоритетах прерываний, условиях появления и условии сброса состояния прерывания приведена ниже в таблице 1.3

Информация о ждущем прерывании Таблица 1.3

| I Type

|

Приоритет

|

Тип

|

Условие появления

|

Условия сброса

|

| 11

|

1

|

Состояние линии приёмника

|

Ошибка переполнения, чётности, посылки или пауза

|

Операция чтения LSR

|

| 10

|

2

|

Доступность принимаемых данных

|

Доступность принимаемых данных

|

Операция чтения RBR

|

| 01

|

3

|

Освобождение регистра буфера передатчика

|

Освобождение THR

|

Операция чтения IIR или запись в THR

|

| 00

|

4

|

Состояние модема

|

Clear To Send, Data Set Ready, Ring Indicator или Data Carrier Detect

|

Операция чтения MSR

|

Бит II является индикатором ждущего прерывания:

0 – контроллер последовательного интерфейса хранит прерывание;

1 – нет прерываний, ожидающих обработки

Биты 7 – 3 регистра не используются и должны принимать

значение 0.

Регистр управления линией (

LCR).

Регистр имеет адрес 3 относительно базового адреса контроллера. Этот регистр доступен по чтению и по записи.

Значение данного регистра определяет формат передаваемых данных в линию передачи данных контроллером последовательного интерфейса. Описание битов регистра приводятся далее.

| 7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| DLAB

|

SB

|

SP

|

EPS

|

PA

|

NSB

|

WLS

|

DLAB управляет доступом к регистрам буфера делителя. Если бит равен 1, операция чтение и запись по адресам – и1 относительно базового адреса выполняются с регистрами буфера делителя программируемого генератора. Для доступа к регистрам RBR, THR и IER бит должен иметь нулевое значение.

SB устанавливает состояние «пауза», когда равен 1. В этом остоянии на выходе контроллера последовательного интерфейса устанавливается значение 0, которое не может быть изменино никакими другими действиями, кроме как переустановка бита в 0.

SP управляет установкой режима неизменимого бита контроля чётности. Значение бита 1 задаёт режим, а значение 0 – отменяет. При установки бита SP в 1 должен устанавливаться в 1 и бит PA, е.е. эти два бита связаны. Когда значение бита EPS равно 0, посылается и контролируется значение бита контроля чётности, равное 1 (Mark Parity). При единичном значении бита EPS посылается и контролируется значение бита контроля чётности, равное 0 (Space Parity).

EPS задаёт выбор режима контроля чётности. Если бит устанговлен в 0 и бит PA установлен в 1, генерируется и проверяется чётное количество единичных битов символа посылки и бита контроля чётности. Если бит установлен в 1 и бит PA установлен в 1, генерируется и проверяется нечётное количество единичных битов символа посылки и бита контроля чётности.

PA является битом разрешения контроля чётности. Если бит установлен в 1, то генерируется бит контроля четности между последним битом передаваемого символа и стоп-битом.

NSB определят количество стоп-битов в каждом символе, передаваемом контроллером последовательного интерфейса, и связан с длинной слова обмена (биты WLS). Если этот бит установлен в 0, то генерируется и проверяется один стоп-бит при любой длине слова обмена. Если этот бит установлен в 1, то при длине слова обмена в 5 бит генерируется и проверяется 1.5 стоп-бита, а при любой другой длине слова обмена генерируется и проверяется 2 стоп-бита[2]

.

Биты WLS определяют длину слова обмена:

00 – 5 битов;

01 – 6 битов;

10 – 7 битов;

11 – 8 битов.

Регистр управления модемом (

MCR).

Регистр управления модемом имеет адрес 4 относительно базового адреса контроллера. Этот регистр доступен по чтению и записи. С помощью регистра можно управлять работой модема.

| 7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| 0

|

0

|

0

|

LB

|

Out2

|

Out1

|

RTS

|

DTR

|

LB задаёт режим «шлейфа» (Loopback) для диагностических целей. При единичной значении этого бита происходит следующее:

· Выход передатчика (SOUT) устанавливается в активное состоние;

· Вход приёмника (SIN) отсоединяется;

· Выход сдвигового регистра передатчика подсоединяется к сдвиговому регистру приёмника;

· Четыре входных управляющих сигналов модема (CTS, DSR, DCD и RI) отсоединяется;

· Черыре выходных управляющих сигнала модема (DTR, RTS, Out1 иOut2) подсоединяются к четырём управляющим вхолдам модема;

· Управляющие цепи модема принудительно устанавливаются в неоктивное состояние.

В диагностическом режиме передаваемые данные сразу же принимаются. При этом полностью обеспечивается прерывание приёмника и передатчика. Управление прерываниями так же управляется регистром IER, однако источниками прерываний в этом случае является четыре младших бита регистра MCR в место четырёх управляющих входов модема. Система управления прерываниями может быть проверена в режиме «шлейф» записью в младшие 6 бит регистра LSR и младшие 4 бита регистра MSR. При установке любого из этих битов в один вырабатывается соответствующие прерывания (если оно разрешено в регистре IER). Условия сброса состояния прерывание полностью соответствуют нормальному режиму работы.

Для возврата к нормальному режиму работы необходимо сначала перепрограммировать регистры для этого режима работы, а затем установить бит LB регистра MCR в значение 0.

Out2 управляет сигналом Out2. При единичном значении бита сигнал Out2 устанавливается равным 1. Сигнал Out2 управляет генерацией прерываний контроллера последовательного интерфейса. При единичном знании сигнал контроллер генерирует прерывание в соответствии со значением регистра IER. При нулевом значении сигнала Out2 контроллер не генерирует прерываний независимо от значение регистра IER.

Out1 управляет сигналом Out1. Если бит установлен в 1, сигнал Out1 устанавливается 1. При задании значения 0 сигнал устанавливается в нулевой уровень.

RTS управляет сигналом «запрос на передачу» (Request to Send). При значении этого бита, равном 1, сигнал «запрос на передачу» устанавливается равным 1. При задании значения 0 сигнал устанавливается в нулевой уровень.

DTR задаёт уровень сигнала «готовность терминала» (Data Terminal Ready). Если бит установлен в 1, сигнал «готовность терминала» устанавливается равным 1. При задании значения 0 сигнал устанавливаться в нулевой уровень.

Биты 7-5 не используются и всегда устанавливаются в 0.

Регистр состояния линии (LSR). Регистр состояние линии имеет адрес 5 относительно базового адреса контроллера и доступен только по чтению. Регистр LSR предоставляет информацию о состоянии обмена данных.

| 7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| 0

|

TEMT

|

THRE

|

BI

|

FE

|

PE

|

OR

|

DR

|

TEMT является индикатором освобождения передатчика .

Установка этого бита в 1 обозначает, что как регистр THR, так и регистр TSR свободный. Этот бит устанавливается в значение 0, если любой из регистров THR и TSR содержит символ.

THRE является индикатором освобождения регистра THR.

Установка этого бита 1 означает, что из регистра THR символ передан в сдвиговый регистр передатчика (TSR) и регистра THR готов принять следующий байт. Если в регистре IER разрешено прерывание по освобождению регистра THR, то при установке этого бита в значении 1 происходит также прерывание по освобождению регистра THR.

BI является индикатором состояния «пауза» (Break Interrupt). Состояние «пауза» фиксируется в том случае, если уровень принимаемого сигнала установлен в 0 на время приёма полной посылке, т.е. общее время стартового бита, битов данных, бита контроля чётности и стоп-бита. Этот бит принимает значение 0 после операции чтении регистра LSR. Биты с 4-1 являются индикаторами ошибки и установка любого из этих битов в значение 1 проводит к порождению прерывания по состоянию линий приёмника.

FE является индикатором «ошибки стоп-битов» (Framing Error).

Ошибка стоп-бита фиксируется в том случае, когда в принятом символе не обнаружена корректного стоп-бита, т.е. бит, следующий за последним битом данных или за битом контроля четности (в случае контроля чётности), имеет значение 0. Этот бит принимает значение 0 после операции чтения регистра LSR.

PE является индикатором «ошибки четности» (Parity Error).

Ошибка четности фиксируется, если в принятом символе обнаружено некорректное значение бита контроля чётности. Этот бит принимает значение 0 после чтении регистра LSR.

OR является индикатором «ошибки переполнения» (Overrun Error). Ошибка переполнения фиксируется в том случае, если при помешении очередного символа в регистр RBR обнаружено, что предедущее содержимое этого регистра не считано и, таким образом, оно потеряно. Этот бит принимает значение 0 после операции чтение регистра LSR.

DR индикатор доступности принимаемых данных. Этот бит всегда устанавливается в 1, когда приёмником полностью принят символ и помещён в регистр RBR. Бит принимает значение 0 после операцией чтения из регистра RBR.

Бит 7 всегда устанавливается в значение 0.

Регистр состояния модема (MSR). Регистр имеет адрес 6 относительно базового адреса контроллера и доступен только по чтению. Регистр предоставляет информацию о состоянии управляющих линий модема. Кроме того, этот регистр содержит 4 бита, которые отображают изменение состояния модема и устанавливаются в значение 0 после операции чтения из регистра MSR.

| 7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| DCD

|

RI

|

DSR

|

CTS

|

DDCD

|

TERI

|

DDSR

|

DCTS

|

DCD является инвертированным сигналом Data Carrier Detect (DCD). При установленном режиме «шлейфа» (бит LB регистра MCR имеет значение 1) этот бит эквивалентен биту Out2 регистра MCR.

RI является инвертированным сигналом Ring Indicator (RI). При установленном режиме «шлейфа» (бит LB регистра MCR имеет значение 1) эквивалентен биту Out1 регистра MCR.

DSR является инвертированным сигналом Data Set Ready (DSR). В режиме «шлейфа» (бит LB регистра MCR имеет значение 1) эквивалентен биту DTR регистра MCR.

CTS – инвертированный сигнал Clear to Send (CTS). При установленном режиме «шлейфа» (бит LB регистра MCR имеет значение 1) этот бит эквивалентен биту RTS регистра MCR.

Биты DDCD, TERI, DDSR и DCTS являются индикаторами изменения состояния модема и установка любого из этих битов в значение 1 приводит к порождению прерывания по состоянию модема, если оно разрешено в регистре IER.

DDCD является индикатором изменения сигнала Data Carrier Detect (DCD). Этот бит принимет значение 1 при изменении сигнала DCD после последней операции чтения регистра MSR.

TERI является индикатором заднего фронта сигнала RI. Этот бит принимает значение 1 при изменении сигнала RI с уровня логической 1 на уровень логического нуля.

DDSR является индикатором изменения сигнала Data Set Ready (DSR). Этот бит принимает значение 1 при изменении сигнала DSR после последней операции чтение регистра MSR.

DTCS является индикатором изменения сигналаClear to Send (CTS). Этот бит принимает значение 1 при изменении сигнала CTS после последней операции чтения регистра MSR.

Не используемый регистр (

Scratch

Register).

Имеет адрес 7 относительно базового адреса контроллера и доступен по чтения и записи. Регистр не управляет контроллерам и может быть использован в качестве рабочего регистра для хранения каких либо данных.

Программируемый генератор. Программируемый генератор служит для установки частоты контроллера последовательного интерфейса. Частота следования определяется как отношение частоты задающего генератора к делителю частоты. Частота задающего генератора равна 1.8432Мгц. делитель частоты представляет собой 16–ти битовое число, младший и старший байт которого загружаются по отдельности через регистры буфера делителя. После операции записи любой из регистров делителя делитель перезагружается сразу же. В таблице 1.4 приведены необходимые значения делителя для получения требуемой частоты следования.

Таблица 1.4

| Требуемая частота

Следования

(в бодах)

|

Значение делителя для получения требуемой частоты следования

|

| В десятичном

Виде

|

В шестнадцатеричном виде

|

| 50

|

2304

|

0900h

|

| 75

|

1536

|

0600h

|

| 150

|

1536

|

0600h

|

| 300

|

384

|

0180h

|

| 600

|

192

|

00C0h

|

| 1200

|

96

|

0060h

|

| 1800

|

64

|

0040h

|

| 2400

|

48

|

0030h

|

| 3600

|

32

|

0020h

|

| 4800

|

24

|

0018h

|

| 7200

|

16

|

0010h

|

| 9600

|

12

|

000Ch

|

| 19200

|

6

|

0006h

|

| 38400

|

3

|

0003h

|

| 57600

|

2

|

0002h

|

| 115200

|

1

|

0001h

|

Последовательная передача данных

Микропроцессорная система без средств ввода и вывода оказывается бесполезной. Характеристики и объемы ввода и вывода в системе определяются, в первую очередь, спецификой ее применения — например, в микропроцессорной системе управления некоторым промышленным процессом не требуется клавиатура и дисплей, так как почти наверняка ее дистанционно программирует и контролирует главный микрокомпьютер (с использованием последовательной линии RS–232C).

Поскольку данные обычно представлены на шине микропроцессора в параллельной форме (байтами, словами), их последовательный ввод–вывод оказывается несколько сложным. Для последовательного ввода потребуется средства преобразования последовательных входных данных в параллельные данные, которые можно поместить на шину. С другой стороны, для последовательного вывода необходимы средства преобразования параллельных данных, представленных на шине, в последовательные выходные данные. В первом случае преобразование осуществляется регистром сдвига с последовательным входом и параллельным выходом (SIPO), а во втором — регистром сдвига с параллельным входом и последовательным выходом (PISO).

Последовательные данные передаются в синхронном или асинхронном режимах. В синхронном режиме все передачи осуществляются под управлением общего сигнала синхронизации, который должен присутствовать на обоих концах линии связи. Асинхронная передача подразумевает передачу данных пакетами

; каждый пакет содержит необходимую информацию, требующуюся для декодирования содержащихся в нем данных. Конечно, второй режим сложнее, но у него есть серьезное преимущество: не нужен отдельный сигнал синхронизации.

Существуют специальные микросхемы ввода и вывода, решающие проблемы преобразования, описанные выше. Вот список наиболее типичных сигналов таких микросхем:

D

0–

D

7

— входные–выходные линии данных, подключаемые непосредственно к шине процессора;

RXD

— принимаемые данные (входные последовательные данные);

TXD

— передаваемые данные (выходные последовательные данные);

CTS

— сброс передачи. На этой линии периферийное устройство формирует сигнал низкого уровня, когда оно готово воспринимать информацию от процессора;

RTS

— запрос передачи. На эту линию микропроцессорная система выдает сигнал низкого уровня, когда она намерена передавать данные в периферийное устройство.

Все сигналы программируемых микросхем последовательного ввода–вывода ТТЛ–совместимы. Эти сигналы рассчитаны только на очень короткие линии связи. Для последовательной передачи данных на значительные расстояния требуются дополнительные буферы и преобразователи уровней, включаемые между микросхемами последовательного ввода–вывода и линией связи.

Протокол

последовательной связи

.

Попытка установить последовательный обмен информацией будет бесполезной, если одно из устройств будет включено. Без принимающего устройства передаваемая информация будет бесследно исчезать в канале. К счастью

RS – 232 в своих спецификациях выделяет 2 проводника для определения подключения к каждому концу последовательного канала устройства и его состояния ( влкючено ли устройство).

Сигнал, передаваемый по 20 контакту, и называется сигналом готовности терминала (Data Terminal ready – DTR). Он имеет позитивную форму с DTE – устройства для сообщения о том, что оно подключено, обеспечено питание и готово начать сеанс связи.

Аналогично сигнал поступает на контакт 6. Он называется сигналом готовности набора данных (Data set ready – DSR). Этот сигнал так же представляется в позитивном виде и говорит о том что DCE - устройство включено и готово к работе.

В нормальном канале RS – 232 оба эти сигнала должны появиться прежде чем произойдет что-либо. Устройство DTE посылает сигнал DTR устройству DSE, и DSE посылает сигнал DSR устройству DTE. Теперь оба устройства знают, что другое устройство готово к работе.

Обычно аппаратное квитирование модема реализуется при помощи двух различных проводников. Устройства DCE устанавливает положительное напряжение в 5 линии, что говорит о готовности к приёму (Clear to send – CTS). Устройство DTE воспринимает этот сигнал как «путь свободен». С другой стороны канала устройство DTE устанавливает положительное напряжение на 4ом контакте. Этот сигнал называется запрос на передачу (Request to Send – RTS ). Он говорит о том, что DCE должно получить информацию.

Важное правило гласит, если оба сигнала и CTS, RTS не представленные положительным напряжением, информация не будет передаваться ни в одном направлении. Если положительное напряжение отсутствует на контакте CTS, устройство DTE не передаст информацию на DCE. Если же положительное напряжение отсутствует в линии RTS, DCE не передаст информацию DTE.

Ещё один сигнал порождается DCE,который необходим для начала передачи информации. Это сигнал определения передачи информации (Carrier Detect или Data Carrier Detect – CD или DCD). Положительное напряжение в этой линии указывает, что модем DCE получил несущий сигнал с модема с другого конца линии. Если же этот сигнал не выявлен, то последовательность импульсов может быть только шумами в линии. Сигналы CD помогаю DTE узнать, когда следует опасаться помех. В некоторых случаях когда CD не имеют положительного потенциала, DTE будет игнорировать поступающую информацию.

Сигнал контакта 22 называется индикатором вызова (Ring Indicator – RI). Он используется модемом DCE для индикации терминалу DTE, к которому он подключен, что им определено напряжение вызова в телефонной линии. Другими словами, положительное напряжение RI будет терминал, сообщая ему, что кто-то тревожит модем. В большинстве последовательных системах связи этот сигнал может считаться параметрическим сигналом, потому что его отсутствие не помешает передаче информации.

Номинально, передаче информации в последовательных каналах предшествует очень жёсткие протокол. Прежде чем она произойдёт, аппаратура на обеих концах каналах должна быть включена и готова к работе. DTE, компьютер подтвердят сигнал DTR и DCE. Модем подтвердит свой DCR. Когда телефонный вызов разбудит модем он пошлёт RI к компьютеру, который может выдать сообщение на экран. Если модем ведет переговоры с другим модемом на другом конце канала, откуда поступил вызов, местный модем сформирует CD сигнал своему компьютеру. Если они не были включены во время ожидания до вызова, компьютер подтвердит RTS, а модем – CTS.

Введите информацию с клавиатуры для посылки её через модем или пошлите информацию из файла. Если модем может передать информацию достаточно быстро, он установит сигнал CTS, прося PС подождать немного. Когда сигнал CTS снова устанавливается положительным, компьютер воспринимает это как приглашение к передаче информации.

Если во время передачи информации у компьютера появится необходимость выполнить какую-либо важную функцию, например, сохранит часть принятой информации на диск, сигнал RTS будет убран, и модем прекратит передачу информации. Когда компьютер освободится, сигнал RTS будет снова установлен и информация будет вновь передаваться через модем.

Интерфейс RS–232C

.

Интерфейс RS–232C является наиболее широко распространенной стандартной последовательной связью между микрокомпьютерами и периферийными устройствами. Интерфейс, определенный стандартом Ассоциации электронной промышленности (

EIA

)

, подразумевает наличие оборудования двух видов: терминального

DTE

и связного

DCE

.

Чтобы не составить неправильного представления об интерфейсе RS–232C, необходимо отчетливо понимать различие между этими видами оборудования. Терминальное оборудование, например микрокомпьютер, может посылать и (или) принимать данные по последовательному интерфейсу. Оно как бы оканчивает (terminate) последовательную линию. Связное оборудование — устройства, которые могут упростить передачу данных совместно с терминальным оборудованием. Наглядным пример связного оборудования служит модем (модулятор–демодулятор). Он оказывается соединительным звеном в последовательной цепочке между компьютером и телефонной линией.

Различие между терминальными и связными устройствами довольно расплывчато, поэтому возникают некоторые сложности в понимании того, к какому типу оборудования относится то или иное устройство. Рассмотрим ситуацию с принтером. К какому оборудованию его отнести? Как связать два компьютера, когда они оба действуют как терминальное оборудование. Для ответа на эти вопросы следует рассмотреть физическое соединение устройств. Произведя незначительные изменения в линиях интерфейса RS–232C, можно заставить связное оборудование функционировать как терминальное. Чтобы разобраться в том, как это сделать, нужно проанализировать функции сигналов интерфейса RS–232C (таблица 1.5).

Таблица 1.5 Функции сигнальных линий интерфейса RS–232C.

| Номер контакта

|

Сокращение

|

Направление

|

Полное название

|

| 1

|

FG

|

—

|

Основная или защитная земля

|

| 2

|

TD

(

TXD

)

|

К DCE

|

Передаваемые данные

|

| 3

|

RD

(

RXD

)

|

К DTE

|

Принимаемые данные

|

| 4

|

RTS

|

К DCE

|

Запрос передачи

|

| 5

|

CTS

|

К DTE

|

Сброс передачи

|

| 6

|

DSR

|

К DTE

|

Готовность модема

|

| 7

|

SG

|

—

|

Сигнальная земля

|

| 8

|

DCD

|

К DTE

|

Обнаружение несущей данных

|

| 9

|

—

|

К DTE

|

(Положительное контрольное напряжение)

|

| 10

|

—

|

К DTE

|

(Отрицательное контрольное напряжение)

|

| 11

|

QM

|

К DTE

|

Режим выравнивания

|

| 12

|

SDCD

|

К DTE

|

Обнаружение несущей вторичных данных

|

| 13

|

SCTS

|

К DTE

|

Вторичный сброс передачи

|

| 14

|

STD

|

К DCE

|

Вторичные передаваемые данные

|

| 15

|

TC

|

К DTE

|

Синхронизация передатчика

|

| 16

|

SRD

|

К DTE

|

Вторичные принимаемые данные

|

| 17

|

RC

|

К DTE

|

Синхронизация приемника

|

| 18

|

DCR

|

К DCE

|

Разделенная синхронизация приемника

|

| 19

|

SRTS

|

К DCE

|

Вторичный запрос передачи

|

| 20

|

DTR

|

К DCE

|

Готовность терминала

|

| 21

|

SQ

|

К DTE

|

Качество сигнала

|

| 22

|

RI

|

К DTE

|

Индикатор звонка

|

| 23

|

—

|

К DCE

|

(Селектор скорости данных)

|

| 24

|

TC

|

К DCE

|

Внешняя синхронизация передатчика

|

| 25

|

—

|

К DCE

|

(Занятость)

|

Примечания:

1. Линии 11, 18, 25

обычно считают незаземленными. Приведенная в таблице спецификация относится к спецификациям Bell 113B и 208A.

2. Линии 9

и 10

используются для контроля отрицательного (

MARK

)

и положительного (

SPACE

)

уровней напряжения.

3. Во избежание путаницы между RD

(Read

— считывать) и RD

(Received

Data

— принимаемые данные) будут использоваться обозначения RXD

и TXD

, а не RD

и TD

.

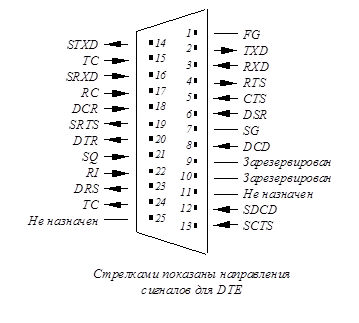

Стандартный последовательный порт RS–232C имеет форму 25–контактного разъема типа D

(рис 1).

Рис. 1. Назначение линий 25–контактного разъема типа

D

для интерфейса RS–232C

Терминальное оборудование обычно оснащено разъемом со штырьками, а связное — разъемом с отверстиями (но могут быть и исключения).

Сигналы интерфейса RS–232C подразделяются на следующие классы.

Последовательные данные

(например, TXD

,

RXD

). Интерфейс RS–232C обеспечивает два независимых последовательных канала данных: первичный (главный) и вторичный (вспомогательный). Оба канала могут работать в дуплексном режиме, т.е. одновременно осуществляют передачу и прием информации.

Управляющие сигналы квитирования

(например, RTS

,

CTS

). Сигналы квитирования — средство, с помощью которого обмен сигналами позволяет DTE

начать диалог с DCE

до фактической передачи или приема данных по последовательной линии связи.

Сигналы синхронизации

(например, TC

, RC

). В синхронном режиме (в отличие от более распространенного асинхронного) между устройствами необходимо передавать сигналы синхронизации, которые упрощают синхронизм принимаемого сигнала в целях его декодирования.

На практике вспомогательный канал RS–232C применяется редко, и в асинхронном режиме вместо 25 линий используются 9 линий

(таблица 1.6).

Таблица 1.6 Основные линии интерфейса RS–232C.

| Номер контакта

|

Сигнал

|

Выполняемая функция

|

| 1

|

FG

|

Подключение земли к стойке или шасси оборудования

|

| 2

|

TXD

|

Последовательные данные, передаваемые от DTE

к DCE

|

| 3

|

RXD

|

Последовательные данные, принимаемые DTE

от DCE

|

| 4

|

RTS

|

Требование DTE

послать данные к DCE

|

| 5

|

CTS

|

Готовность DCE

принимать данные от DTE

|

| 6

|

DSR

|

Сообщение DCE

о том, что связь установлена

|

| 7

|

SG

|

Возвратный тракт общего сигнала (земли)

|

| 8

|

DCD

|

DTE

работает и DCE

может подключится к каналу связи

|

Виды сигналов

В большинстве схем, содержащих интерфейс RS–232C, данные передаются асинхронно, т.е. в виде последовательности пакета данных. Каждый пакет содержит один символ кода ASCII, причем информация в пакете достаточна для его декодирования без отдельного сигнала синхронизации.

Символы кода ASCII представляются семью битами, например буква А

имеет код 1000001. Чтобы передать букву А

по интерфейсу RS–232C, необходимо ввести дополнительные биты, обозначающие начало и конец пакета. Кроме того, желательно добавить лишний бит для простого контроля ошибок по паритету (четности).

Наиболее широко распространен формат, включающий в себя один стартовый бит, один бит паритета и два стоповых бита. Начало пакета данных всегда отмечает низкий уровень стартового бита. После него следует 7 бит данных символа кода ASCII. Бит четности содержит 1 или 0 так, чтобы общее число единиц в 8–битной группе было нечетным. Последним передаются два стоповых бита, представленных высоким уровнем напряжения. Эквивалентный ТТЛ–сигнал при передаче буквы А

показан на рис. 2.

Рис. 2. Представление кода буквы А сигнальными уровнями ТТЛ.

Таким образом, полное асинхронно передаваемое слово состоит из 11 бит (фактически данные содержат только 7 бит) и записывается в виде 01000001011.

Используемые в интерфейсе RS–232C уровни сигналов отличаются от уровней сигналов, действующих в компьютере. Логический 0 (

SPACE

)

представляется положительным напряжением в диапазоне от +3 до +25 В, логическая 1 (

MARK

)

— отрицательным напряжением в диапазоне от –3 до –25 В. На рис. 3 показан сигнал в том виде, в каком он существует на линиях TXD

и RXD

интерфейса RS–232C.

Рис. 3. Вид кода буквы А на сигнальных линиях

TXD

и RXD

.

Сдвиг уровня, т.е. преобразование ТТЛ–уровней в уровни интерфейса RS–232C и наоборот производится специальными микросхемами драйвера линии и приемника линии

.

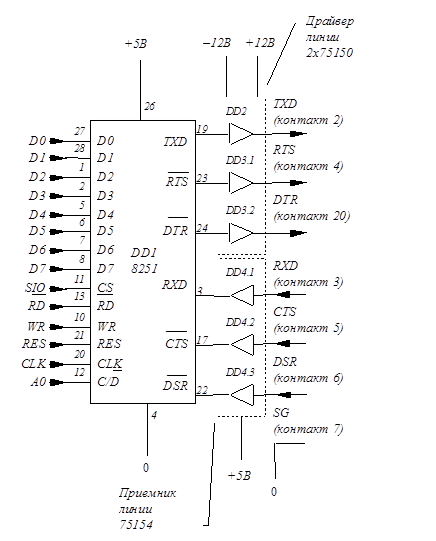

На рис. 4 представлен микрокомпьютерный интерфейс RS–232C. Программируемая микросхема DD

1

последовательного ввода осуществляет параллельно–последовательные и последовательно–параллельные преобразования данных. Микросхемы DD

2

и DD

3

производят сдвиг уровней для трех выходных сигналов TXD

,

RTS

,

DTR

, а микросхема DD

4

— для трех входных сигналов RXD

,

CTS

,

DSR

. Микросхемы DD

2

и DD

3

требуют напряжения питания ±12 В.

Рис. 4. Схема интерфейса RS–232C.

Усовершенствования

Разработано несколько новых стандартов, направленных на устранение недостатков первоначальных спецификаций интерфейса RS–232C. Среди них можно отметить интерфейс RS–422 (балансная система, допускающая импеданс линии до 50 Ом), RS–423 (небалансная система с минимальным импедансом линии 450 Ом) и RS–449 (стандарт с высокой скоростью передачи данных, в котором несколько изменены функции схем и применяется 37–контактный разъем типа D

).

Тестирование канала RS–232C

Соединители

. Эти дешевые устройства упрощают перекрестные соединения сигнальных линий интерфейса RS–232C. Они обычно оснащаются двумя разъемами типа D

(или ленточными кабелями, имеющими розетку и вставку), и все линии проводятся к той области, куда можно вставить перемычки. Такие устройства включаются последовательно с линиями интерфейса RS–232C, и затем проверяются различные комбинации подключений.

Трансформаторы разъема

. Обычно эти приспособления имеют разъем RS–232C со штырьками на одной стороне и разъем с отверстиями на другой стороне.

Пустые модемы

. Как и предыдущие устройства, пустые модемы включаются последовательно в тракт данных интерфейса RS–232C. Их функции заключаются в изменении сигнальных линий таким образом, чтобы превратить DTE

в DCE

.

Линейные

мониторы

. Мониторы индицируют логические состояния (в терминах MARK

и SPACE

) наиболее распространенных сигнальных линий данных и квитирования. С их помощью пользователь получает информацию о том, какие сигналы в системе присутствуют и активны.

Врезки

. Эти устройства обеспечивают доступ к сигнальным линиям. В них, как правило, совмещены возможности соединителей и линейных мониторов и, кроме того, предусмотрены переключатели или перемычки для соединения линий с обоих сторон устройства.

Интерфейсные

тестеры

. По своей конструкции эти устройства несколько сложнее предыдущих простых устройств. Они позволяют переводить линии в состояния MARK

или SPACE

, обнаруживать помехи, измерять скорость передачи данных и индицировать структуру слова данных.

Использованная литература

1. Тули М.

Справочное пособие по цифровой электронике

: Пер. с англ. — М.: Энергоатомиздат, 1990.

2. Справочник программиста и пользователя

/ Под ред. А. Г. Шевчика, Т. В. Демьянкова

. — М.: “Кварта”, 1993.

3. Справочник Вегнер В.А.

[1]

В таблице приведено значение бита DLAB регистра LCR, который управляет адресацией регистров. Именно этот бит делает возможным доступ к разным регистрам контроллера через порты с одним адресом. В приведённой таблице в графе «DLAB» стоит символ «X», если для адресации соответствующего регистра состояние данного бита несущественно.

[2]

При асинхронной передаче понятие бита неразрывно связано с длительностью сигнала, поэтому вполне возможна посылка нецелого числа стоп-битов. Это может потребоваться, если подключенное к компьютеру устройство не программируется, а жестко настроено на анализ стоп-битов заданной длительности.

|