| Московский государственный институт электроники и математики

(технический университет)

Кафедра ИКТ

Курсовая работа

по дисциплине “Информатика”

на тему:

“Последовательный сумматор.”

Выполнил:

студент группы С-14

Попов С.И.

Проверил:

Сафонов С.Н.

Москва – 2009

Аннотация.

В данной курсовой работе представлены теоретические сведения о сумматорах и их классификации. Подробно разобран последовательный сумматор и принцип его работы.

Краткие теоретические сведения.

Сумматор – это электронный узел, предназначенный для выполнения микрооперации арифметического сложения (суммирования) двух чисел (слов). При сложении двух чисел, представленных в виде двоичных кодов A (a0

, a1

,… an

) и B (b0

, b1

,… bn

) образуется сумма S (s0

, s1

,… sn

). Значение i-x разрядов образуется в соответствии с правилом:

Si

=ai

+bi

+pi

-1

; pi

=0 – при (ai

+bi

+pi

-1

) < q, Si

=ai

+bi

+pi

-1

; pi

=1 – при (ai

+bi

+pi

-1

) >= q,

где: Si

– сумма в i‑м разряде, pi

-1

– перенос из соседнего младшего разряда, q – основание системы счисления.

Одна из важных характеристик сумматора – разрядность. Разряды подразделяются на знаковые и цифровые. Знаковые разряды содержат знак числа, цифровые содержат число, над которым выполняется операция сложения.

Существуют три основных кода представления чисел: прямой, обратный и дополнительные. При переводе из одного кода в другой изменяются только цифровые разряды. Знаковые разряды остаются постоянными в любом коде.

Сумматор выполняет сложение чисел в обратном коде. В случае, если после сложения знаковые разряды отличаются, фиксируется переполнение. В процессе схемотехнического проектирования сумматора были учтены такие особенности устройств последовательного действия, как подача синхросигнала и согласование временных задержек.

Сумматоры классифицируют:

– По принятой системе счисления и кодирования различают: двоичные, двоично-десятичные, десятичные и др;

– В зависимости от количества входов и выходов бывают: сумматоры по модулю 2, полусумматоры и полные сумматоры;

– По способу организации процесса суммирования одноразрядной суммирующей схемы: комбинационного типа, накапливающего типа и комбинированные;

– По способу организации цепей переноса между разрядами: с последовательным, с параллельным, с групповым и с одновременным переносами;

Реклама

– По способу обработки многоразрядных чисел различают: последовательные, параллельные и комбинированные.

Для сложения многоразрядных чисел сумматор представляет собой набор одноразрядных сумматоров, имеющих входы для слагаемых и переноса из младшего разряда и выходы суммы и переноса в старший разряд.

Выбор и обоснование элементной базы.

1. Полный одноразрядный сумматор УГО:

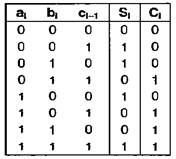

Таблица истинности одноразрядного сумматора.

Выполняет суммирование одноразрядных чисел.

2. D Триггер.

Триггеры-элементарные автоматы, содержащие элемент памяти(фиксатор) и схему управления.

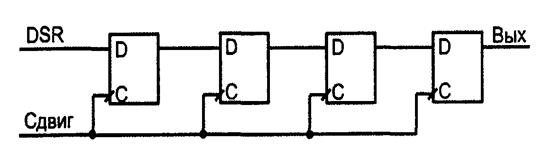

3.Регистр сдвига вправо.

Регистры сдвига представляют собой цепочку разрядных схем связанных цепями переноса.

Принцип действия устройства.

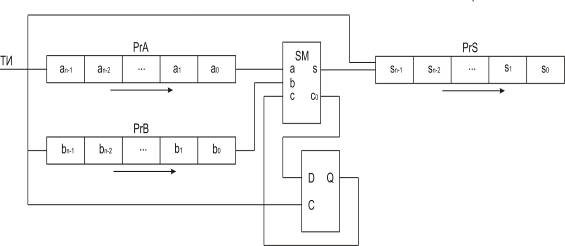

Сумматор для последовательных операндов содержит всего один одноразрядный сумматор, обрабатывающий числа последовательно разряд за разрядом, начиная с младшего. Сложив младшие разряды (a0

и b0

), одноразрядный сумматор вырабатывает сумму (s0

) для младшего разряда результата и перенос (c0

), который запоминается на один такт.

В следующем такте складываются вновь поступившие разряды слагаемых (a1

и b1

) с переносом из младшего разряда (с0

) и т.д. Условная схема последовательного n‑разрядного сумматора (рис. 1), помимо одноразрядного двоичного сумматора, содержит сдвигающие регистры слагаемых и суммы, а также триггер, запоминающий перенос. Регистры и триггер тактируются сигналом ТИ.

Рис.1

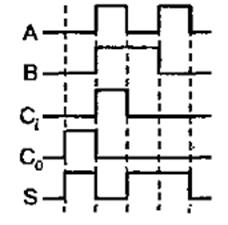

Рис.2

Рис. 1. Схема последовательного n‑разрядного сумматора.

Рис.2. временная дмаграмма соответствующая операции сложения двух операндов 101+110=1011 или в десятичном выражении 5+6=11.

Список литературы.

1.Угрюмов Е.П. Цифровая схемотехника.- СПб.: БХВ-Петербург, 2002 – 528 с.:ил.ISBN 5-8206-0100

2.http://ru.wikipedia.org/wiki/%D0%A1%D1%83%D0%BC%D0%BC%D0%B0%D1%82%D0%BE%D1%80

|