Микроконтроллеры семейства

Z

86 фирмы

ZILOG

ВВЕДЕНИЕ

Устройства передачи и обработки информации являются теми "кирпичами", из которых строятся сложные информационно-управляющие системы, такие как, например, цифровые сети связи с интеграцией служб -ISDN [1]. Проектирование таких устройств представляет сложную техническую задачу, поскольку к ним предъявляется ряд серьезных технических требований в части:

- сложных протоколов обмена данными;

- высоких скоростей передачи;

- сложных алгоритмов обработки;

- высокой точности;

- аналого-цифровых функций;

- надежности и достоверности;

- устойчивости к воздействию дестабилизирующих факторов;

- конструктивных параметров (габаритные размеры, масса);

- энергопотребления.

Решающую роль на технические характеристики устройств передачи и обработки информации оказывает используемая элементная база. Наиболее подходящая элементная база для построения таких устройств -это однокристальные микроконтроллеры (МК). Такие приборы поставляются на мировой рынок всеми ведущими производителями микропроцессоров: Intel, Motorola, Texas Instruments, Microchip Technology, Zilog и др. Особый интерес для рассматриваемого класса устройств представляют малогабаритные МК с микромощным потреблением. Среди них можно выделить МК PIC 16CXX фирмы Microchip Technology [2] и Z8 фирмы Zilog [3,4]. Если PIC-контроллеры относятся к процессорам с так называемой сокращенной системой команд (Reduced Instruction Set Command -RISC), то Z8 -это процессоры с комплексной системой команд (Complex Instruction Set Command -CISC). Преимуществом последних является более высокий уровень команд, что делает программный код более эффективным в смысле времени выполнения и объема занимаемой памяти и упрощает программирование на языке ассемблера. Это позволяет рекомендовать MK семейства Z8 для использования в практике проектирования устройств передачи и обработки информации.

В настоящем пособии подробно рассмотрены вопросы архитектурного построения и программирования МК семейства Z8, а также примеры проектирования устройств передачи и обработки информации на базе этих МК.

1. Однокристальные микроконтроллеры семейства Z8

1.1. Описание семейства Z8

Реклама

Среди новейших моделей МК семейства Z8 следует выделить ряд малопотребляющих МК, выполненных по КМОП технологии, основные параметры которых приведены в табл.1.1. Обозначение МК состоит из префикса фирмы -Z, номера семейства -86, литеры исполнения и номера модели.

Таблица 1.1

Малопотребляющие микроконтроллеры семейства Z8

Обозначение

Микросхемы

|

ПЗУ

Байт

|

ОЗУ

байт

|

Ввод/Вывод

Бит

|

Частота

МГц(max)

|

Корпус

к-во выв.

|

| Z86x02 |

512 |

61 |

14 |

8 |

18 |

| Z86x03 |

512 |

61 |

14 |

8 |

18 |

| Z86x04 |

1K |

125 |

14 |

12 |

18 |

| Z86x06 |

1K |

125 |

14 |

12 |

18 |

| Z86x08 |

2K |

125 |

14 |

12 |

18 |

| Z86x31 |

2K |

125 |

24 |

16 |

28 |

| Z86x30 |

4K |

237 |

24 |

16 |

28 |

| Z86x40* |

4K |

236 |

32 |

16 |

40/44 |

Примечание:х - литера исполнения, С, Е или L.

* - имеется возможность подключения внешних ПЗУ и ОЗУ объемом по 60К байт.

МК, в обозначение которых входит литера "C", имеют ПЗУ с масочным программированием. Литера "E" в обозначении указывает на вариант с однократно электрически программируемым ПЗУ. Литера "L" соответствует вариантам с масочным ПЗУ и пониженным напряжением питания. Первые используют для выпуска серийных изделий (5000 и более штук), вторые -для опытных, единичных и мелкосерийных изделий, третьи -для серийных устройств с автономным питанием от пары сухих гальванических элементов или аккумуляторов.

Фирма-изготовитель поставляет специальное недорогое оборудование в виде аппаратно-программных кросс-средств, ориентированных на ПЭВМ IBM PC, для разработки изделий на базе МК, куда входит и программатор для однократно программируемых МК ( например, внутрисхемный эмулятор -программатор Z86CCP01ZEM с программным обеспечением ).

Все МК [4,5] имеют 5 -6-и уровневый контроллер прерываний, один или два таймера/счетчика и два аналоговых компаратора. Последние позволяют решать вопросы сравнения уровней напряжения, детектирования короткозамкнутого состояния датчиков, аналого-цифрового преобразования без использования дополнительных компонентов. Кроме того, модель 06 имеет встроенный последовательный интерфейс.

Линии ввода/вывода МК обеспечивают совместимость с КМОП -уровнями. Выходные усилители под управлением программного обеспечения могут конфигурироваться как двухтактные или с открытым стоком. Кроме того, для исключения резкого возрастания тока, потребляемого входными КМОП ключами при отсутствии источника входного уровня, все цифровые входы снабжены автофиксаторами уровня (Auto Latch). В последних версиях МК автофиксаторы могут отключаться, что повышает совместимость входов ( особенно для аналоговых линий).

Разработчики МК предусмотрели в них целый ряд аппаратных функций, обеспечивающих надежность работы в условиях воздействия помех и дестабилизирующих факторов: автоматический сброс при включении питания (Power-On Reset), сторожевой таймер (Watch-Dog Timer), защита от снижения напряжения питания (Low-Voltage Protection), защита ОЗУ (RAM Protect).

Реклама

Автоматический сброс при включении питания обеспечивается специальным таймером сброса, синхронизируемым от встроенного RC-генератора. Этот таймер обеспечивает удержание процессора в состоянии сброса, пока питающее напряжение не достигнет номинального уровня, а генератор основной синхронизации не выйдет на стабильный режим.

Сторожевой таймер защищает процессор от "зависания". Управляется он программно специальными командами. При "зависании" программы очередная команда перезапуска сторожевого таймера не выполнится, он досчитает до конца и вызовет функцию сброса МК -тем самым вычислительный процесс будет восстановлен.

Функция защиты от снижения напряжения питания позволяет обеспечить корректное возобновление вычислительного процесса при "провалах" питающего напряжения.

Сущность защиты ОЗУ заключается в возможности программно управлять доступом к определенной области ОЗУ, содержащей управляющую информацию. Запрещение доступа гарантирует сохранение этой информации и правильное ее использование в случае, например, сбоя программного счетчика, в результате которого может произойти некорректное обращение к этой области ОЗУ и искажение управляющей информации.

МК работают в широком диапазоне питающих напряжений:

3 -5,5В -для масочного исполнения; 4,5 -5,5В -для однократно программируемого и 2 -3,9В -для исполнения с пониженным питающим напряжением. Потребляемая мощность в стандартном режиме на максимальной допустимой частоте составляет 30 -60 мВт.

Для целей экономии потребляемой мощности предусмотрено также два резервных режима с микропотреблением: HALT и STOP. В первом режиме отключается синхронизация процессора, активными остаются лишь таймеры/счетчики и прерывания. Во втором режиме отключается и синхрогенератор, только сторожевой таймер может продолжать свою работу.

Оригинальная схема встроенного генератора синхронизации позволяет использовать в качестве времязадающих элементов кварцевые и керамические резонаторы, LC и RC-цепи. Возможна и синхронизация от внешнего источника. Функционирование МК обеспечивается в широком диапазоне рабочих частот от 10 кГц до максимальной (см. табл.1.1). Причем, чем ниже частота, тем меньше потребляемый ток от источника питания. Например, для версии "C" большинства МК на частоте 32 кГц гарантируется потребляемый ток 8 мкА.

Для применений с высокими требованиями к электромагнитной совместимости МК Z8 могут быть переведены в малошумящий режим (Low Noise). В этом режиме несколько ухудшается нагрузочная способность портов вывода и увеличивается время переходных процессов, однако значительно снижается уровень электромагнитного излучения. Частота внешнего кварцевого резонатора при этом ограничивается величиной 4 МГц.

Изготовитель гарантирует надежную работу МК при температуре окружающей среды от 0 до 70 градусов Цельсия для стандартного исполнения и от -40 до 105 градусов для исполнения с расширенным температурным диапазоном (Extended Temperature). В последнем исполнении поставляются все МК с литерой "C" и модели 02, 04, 08, 30, 31 и 40 с литерой "E".

И, наконец, для исключения возможности копирования программы МК конкурентами предусмотрен, бит защиты ПЗУ (ROM Protect). В более ранних версиях МК установка бита защиты запрещала команды загрузки из ПЗУ (LDC и LDCI), что одновременно заставляло программиста отказываться от использования весьма эффективных алгоритмов, основанных на просмотре таблиц. В последних версиях МК доступ к ПЗУ блокируется установкой бита защиты без запрета указанных команд и каких-либо алгоритмических ограничений.

1.2. Архитектура микроконтроллеров Z8

1.2.1. Структурная схема микроконтроллеров

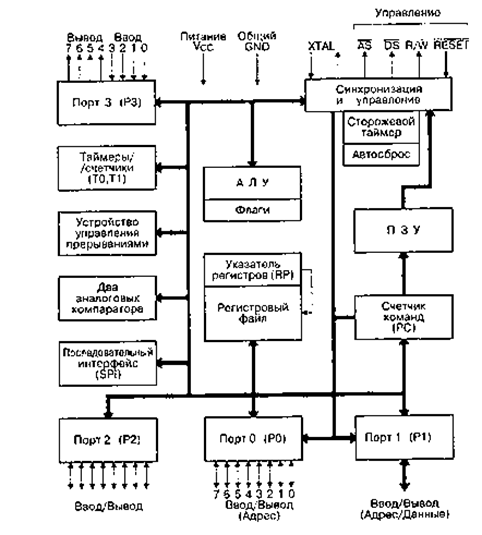

На рис.1.1 приведена обобщенная структурная схема МК, а в табл. 1.2 указаны наборы вариативных элементов структуры для каждой модели.

Рис. 1.1 Обобщенная структурная схема микроконтроллеров Z8

Согласно структуре МК, рис.1.1, операционное устройство представлено арифметико-логическим узлом (АЛУ) и флаговым регистром. Устройство управления МК содержит счетчик команд PC (Program Counter) и узел синхронизации и управления со сторожевым таймером и схемой автосброса. Система памяти МК представлена постоянным запоминающим устройством (ПЗУ) для хранения программ и оперативной памятью для данных и стека, выполненной в виде регистрового файла. Для сокращения размера поля адреса регистрового файла он поделен на рабочие группы. Номер активной группы задается специальным указателем регистров RP (Register Poitner). Модель 40 имеет возможность расширения объема памяти до 64 Кбайт путем подключения внешней памяти программ и данных.

Таблица 1.2

Параметры структуры рис.1.1 для моделей микроконтроллеров Z8

| Модель |

Узлы |

Выводы |

| T0 |

T1 |

SPI |

Управление |

Порт P0

76543210

|

Порт P1 |

Порт P3

76543210

|

| 02 |

- |

* |

- |

- |

*** |

- |

*** |

| 03 |

- |

* |

- |

- |

- |

- |

****** |

| 04 |

* |

* |

- |

- |

*** |

- |

*** |

| 06 |

* |

* |

* |

- |

- |

- |

****** |

| 08 |

* |

* |

- |

- |

*** |

- |

*** |

| 31 |

* |

* |

- |

- |

******** |

- |

******** |

| 30 |

* |

* |

- |

- |

******** |

- |

******** |

| 40 |

* |

* |

- |

* |

******** |

* |

******** |

Устройство ввода/вывода МК представлено 4 программируемыми портами. Кроме того, на кристалле МК выполнен ряд периферийных устройств: 1- таймера/счетчика, устройство управления прерываниями, 2 аналоговых компаратора и последовательный интерфейс SPI (Serial Peripheral Interface). Назначение выводов микроконтроллера понятно из рис.1 за исключением выводов узла синхронизации и управления, функции которых пояснены ниже:

XTAL -выводы для подключения кварцевого или керамического резонатора, LC- или RC-цепи;

/AS -выход строба адреса (Address Strobe);

/DS -выход строба данных (Data Strobe);

R//W -сигнал "Чтение//Запись"(Read//Write);

/RESET- вход сброса.

Примечание. Здесь и далее для сигналов с низким активным уровнем используются два эквивалентных обозначения, например:

__

AS или /AS.

Физическое наличие определенных узлов и выводов в разных моделях МК отмечено в табл.1.2 знаком "*".

1.2.2. Адресное пространство микроконтроллеров

Адресное пространство МК состоит из адресного пространства регистрового файла и адресного пространства памяти. В адресное пространство регистрового файла включены периферийные регистры, управляющие регистры, порты ввода/вывода и регистры общего назначения (РОН). Последние образуют ОЗУ МК. Адресное пространство памяти образовано ячейками внутренней и внешней памяти программ для хранения программного кода и констант, а также ячейками внешней памяти данных для хранения данных и размещения стека.

1.2.2.1. Адресное пространство регистрового файла

Регистровый файл состоит из стандартного регистрового файла (СРФ), имеющегося во всех моделях МК, и расширенного регистрового файла (РРФ), частично используемого в некоторых моделях МК для управления дополнительными функциями.

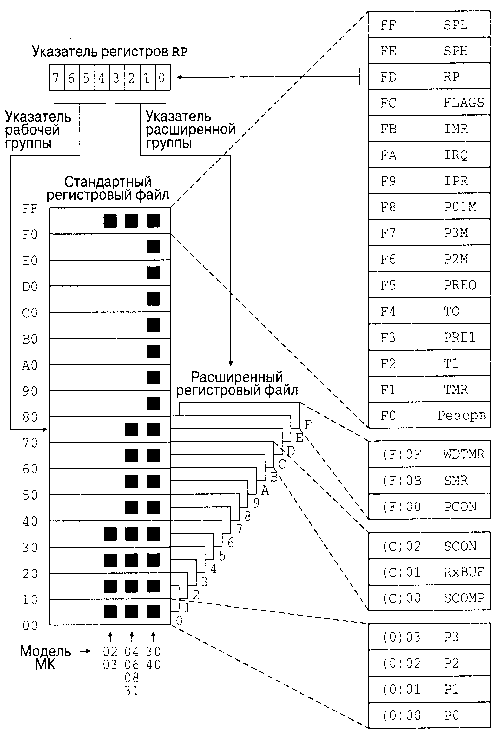

Структура регистрового файла показана на рис 1.2.

СРФ состоит из 256 восьмибитных регистров с шестнадцатеричными адресами от 00H до FFH (здесь и далее H -суффикс шестнадцатеричной системы счисления). Адресное пространство СРФ разделено на 16 рабочих групп регистров по 16 регистров в каждой. Рабочая группа 0 содержит регистры с адресами от 00H до 0FH, группа 1 -регистры с адресами от 10H до 1FH и т.д. Следовательно, правомерно считать, что первая шестнадцатеричная цифра адреса соответствует номеру рабочей группы регистров, а вторая -номеру регистра. На рис.1.2 выделены рабочие группы регистров СРФ с указанием адреса нулевого регистра каждой группы в шестнадцатеричной системе счисления.

Рабочая группа регистров 0 -особая, она может замещаться группами регистров из РРФ. РРФ содержит 16 расширенных групп регистров по 16 регистров в каждой. На рис.1.2 указаны номера расширенных регистровых групп. Следует отметить, что рабочая группа 0 СРФ совпадает с расширенной группой 0 РРФ.

Специальный регистр RP (Register Pointer -Указатель регистров), размещенный в СРФ по адресу FDH (253), содержит два четырехбитных указателя, определяющие текущие номера рабочей (старшая тетрада) и расширенной (младшая тетрада) регистровых групп. Перезагрузкой регистра RP можно оперативно изменять выбранные группы регистров. Старшая цифра указанного в команде загрузки шестнадцатеричного числа будет определять номер рабочей группы, а младшая -номер расширенной группы регистров.

Доступ к регистрам может осуществляться как с помощью полного восьмибитного адреса, так и с помощью короткого четырехбитного адреса. В последнем случае адрес определяет номер регистра в текущей рабочей группе. Если текущая рабочая группа -0, то будет выбран соответствующий регистр из текущей расширенной группы. В случае использования восьмибитного адреса 0XH (где X -любая шестнадцатеричная цифра) выбирается регистр X текущей расширенной регистровой группы, а адреса 1XH -FXH соответствуют регистрам СРФ. В последнем случае исключение составляет рабочая группа регистров E (адреса E0H -EFH), к которой нельзя обращаться с помощью восьмибитного адреса, т.к. байтовый формат EXH зарезервирован разработчиками МК для команд с укороченным адресом.

Разные модели МК имеют разные наборы физически доступных регистровых групп. Для СРФ эти наборы показаны на рис.1.2 столбиковой диаграммой. Расширенная группа регистров 0 (она же -рабочая группа регистров 0) имеется во всех моделях МК. Расширенная группа регистров C имеется только в модели 06, а расширенная группа регистров F имеется в моделях 03,06,30,31,40. Незадействованные регистры расширенных групп 1 -F зарезервированы разработчиками МК для дальнейших применений.

Рис. 1.2 Структура регистрового файла

Часть регистров СРФ имеет специальное назначение (управляющие и периферийные регистры), остальная часть -регистры общего назначения -РОН (General Purpose Register -GPR). Последние и образуют оперативное запоминающее устройство (ОЗУ) МК. Регистры специального назначения сосредоточены в рабочей группе F и в расширенной/рабочей группе 0. Все задействованные регистры расширенных групп имеют специальное назначение. На рис. 1.2 справа показаны все регистры специального назначения. Для каждого регистра указаны шестнадцатеричный адрес и идентификатор, представляющий аббревиатуру назначения регистра. В табл. 1.3 приведен полный перечень этих регистров с указанием идентификатора, назначения на английском и русском языках и характера операций доступа (R -чтение, W -запись).

Таблица 1.3

Регистры специального назначения

| Идентификатор |

Назначение |

Доступ |

| Английский |

Русский |

| SPL |

Stack Pointer Low Byte |

Указатель стека - мл. байт |

R/W |

| SPH |

Stack Pointer High Byte |

Указатель стека - ст. байт |

R/W |

| RP |

Register Pointer |

Указатель регистров |

R/W |

| FLAGS |

Program Control Flags |

Регистр флагов |

R/W |

| IMR |

Interrupt Mask Register |

Регистр маски прерываний |

R/W |

| IRQ |

Interrupt Request Register |

Регистр запросов прерываний |

R/W |

| IRP |

Interrupt Priority Register |

Регистр приоритета прерываний |

W |

| P01M |

Port 0-1 Mode Register |

Регистр режима портов 0-1 |

W |

| P3M |

Port 3 Mode Register |

Регистр режима порта 3 |

W |

| P2M |

Port 2 Mode Register |

Регистр режима порта 2 |

W |

| PRE0 |

TO Prescaler |

Предделитель ТО |

W |

| TO |

Timer/Counter TO |

Таймер/Счетчик ТО |

R/W |

| PRE1 |

T1 Prescaler |

Предделитель Т1 |

W |

| T1 |

Timer/Counter T1 |

Таймер/Счетчик Т1 |

R/W |

| TMR |

Timer Mode Register |

Регистр режимов таймеров |

R/W |

| WDTMR |

Watch Dog Timer Mode Register |

Регистр режима сторожевого таймера |

W |

| SMR |

Stop-Mode Recovery Register |

Регистр управления восстановлением из режима STOP |

W* |

| PCON |

Port Control Register |

Регистр управления портами |

W |

| SCON |

SPI Control Register |

Регистр управления последовательным интерфейсом |

R/W |

| RxBUF |

SPI Receive Buffer |

Приемный буфер последовательного интерфейса |

R/W |

| SCOMP |

SPI Compare Register |

Регистр сравнения последовательного интерфейса |

R/W |

| P3 |

Port 3 |

Порт 3 |

R/W |

| P2 |

Port 2 |

Порт 2 |

R/W |

| P1 |

Port 1 |

Порт 1 |

R/W |

| P0 |

Port 0 |

Порт 0 |

R/W |

* Бит 7 регистра SMR - только для чтения.

Наборы регистров специального назначения для разных моделей МК приведены в табл.1.4.

Таблица 1.4

Наборы регистров специального назначения

| Имя Регистра |

Модель МК |

| 02 |

03 |

04 |

06 |

08 |

31 |

30 |

40 |

| SPL |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| SPH |

* |

* |

* |

* |

* |

* |

* |

+ |

| RP |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| FLAGS |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| IMR |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| IRQ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| IPR |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| P01M |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| P3M |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| P2M |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| PRE0 |

- |

- |

+ |

+ |

+ |

+ |

+ |

+ |

| T0 |

- |

- |

+ |

+ |

+ |

+ |

+ |

+ |

| PRE1 |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| T1 |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| TMR |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| WDTMR |

- |

+ |

- |

+ |

- |

+ |

+ |

+ |

| SMR |

- |

+ |

- |

+ |

- |

+ |

+ |

+ |

| PCON |

- |

+ |

- |

+ |

- |

+ |

+ |

+ |

| SCON |

- |

- |

- |

+ |

- |

- |

- |

- |

| RxBUF |

- |

- |

- |

+ |

- |

- |

- |

- |

| SCOMP |

- |

- |

- |

+ |

- |

- |

- |

- |

| P3 |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| P2 |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

| P1 |

- |

- |

- |

- |

- |

- |

- |

+ |

| P0 |

+ |

- |

+ |

- |

+ |

+ |

+ |

+ |

Примечания:1.Наличие регистра отмечено знаком "+".

2.Регистр SPH во всех моделях, кроме 40, используется как

регистр общего назначения GPR (отмечено знаком "*").

При программировании МК следует учитывать способ доступа к регистрам. Чтение регистров, предназначенных только для записи, будет давать результат FFH. Поэтому использование этих регистров в командах, где они считываются (например, в логических командах OR и AND), будет давать неправильный результат. Когда линии портов 0 и 1 определены как выходы адреса, они приобретают статус регистров только для записи. И, наконец, регистр WDTMR должен быть записан в течение первых 64 тактов синхронизации после сброса.

РОНы, с точки зрения системы команд, могут рассматриваться не только как отдельные восьмибитные регистры, но и как шестнадцатибитные пары регистров. При этом должно соблюдаться четное выравнивание, т.е. адрес регистровой пары должен быть четный. При этом старший байт регистровой пары размещается по четному адресу, а младший -по нечетному. В рабочей регистровой группе регистровых пар будет 8, и им соответствуют только четные номера: 0,2,...,14.

Доступ к отдельным битам регистров осуществляется логическими командами с масками.

Функция защиты ОЗУ заключается в том, что старшая часть адресного пространства от 80H до EFH (исключая управляющую группу регистров) может быть защищена от чтения и записи. Бит защиты ОЗУ программируется одновременно с ПЗУ (масочно или электрически). Если этот бит запрограммирован, то функция защиты управляется программно битом D6 регистра IMR. Логическая 1 включает функцию защиты, логический 0 -отключает. Эту функцию имеют только модели МК 30 и 40.

1.2.2.2. Адресное пространство памяти

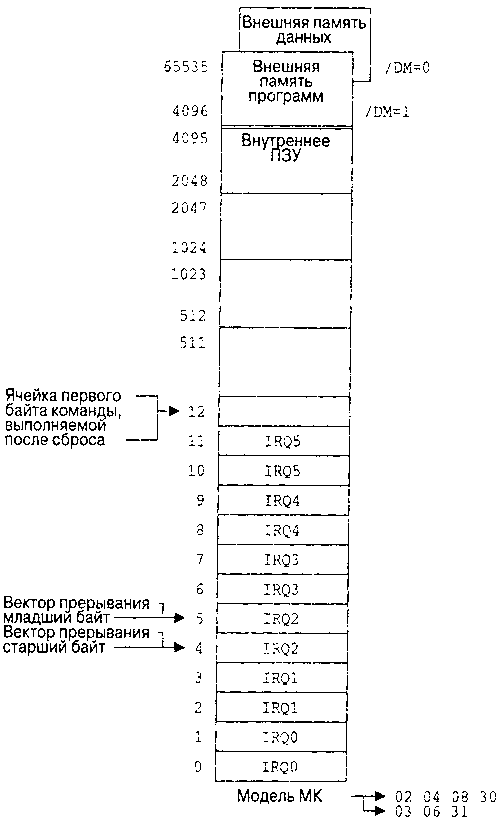

Адресное пространство памяти состоит из адресного пространства памяти программ и адресного пространства памяти данных. Память программ состоит из внутреннего ПЗУ и внешней памяти. Память данных также является внешней. Структура адресного пространства памяти МК показана на рис.1.3. Доступность фрагментов адресного пространства для различных моделей МК показана на рисунке столбиковой диаграммой.

Рис. 1.3 Структура памяти

Внутреннее ПЗУ имеют все рассматриваемые модели МК. Модели с литерами C и L имеют масочное ПЗУ, а модели с литерой E -однократно -программируемое (One Time Programmable -OTP) ПЗУ. Размер внутреннего ПЗУ составляет для разных моделей МК от 512 байт до 4 Кбайт. Первые 12 байт зарезервированы для векторов прерываний (см. рис.1.3). Эти ячейки содержат 6 шестнадцатибитных векторов прерываний, которые соответствуют 6 возможным запросам прерывания: IRQ0 -IRQ5 (Interrupt Request). Начиная с ячейки 12 (0CH) размещается программа.

Модель 40 имеет возможность подключения внешней памяти программ объемом до 60 Кбайт. Такое подключение возможно с использованием мультиплексных линий адреса/данных (AD7 -AD0) порта 1 и адресных линий (A15 -A8) порта 0. Максимальный адрес внешней памяти программ -65535 (FFFFH). Этот интерфейс внешней памяти поддерживается управляющими линиями /AS, /DS и R//W. Доступ к памяти программ (в том числе и к внешней) осуществляется с помощью программного счетчика для считывания команд, а также командами загрузки констант LDC и LDCI.

Модель 40 также имеет возможность дополнительно адресовать до 60 Кбайт внешней памяти данных с адресами от 4096 (1000H) до 65535 (FFFFH) путем программирования выхода порта 3 P34 на выдачу сигнала /DM (Data Memory), позволяющего аппаратно разделить адресные пространства внешней памяти программ и внешней памяти данных. Обращение к внешней памяти данных осуществляется специальными командами загрузки LDE и LDEI, при исполнении которых сигнал /DM будет иметь активный низкий уровень.

В МК предусмотрен специальный бит защиты ПЗУ (ROM Protect), который программируется одновременно с внутренней памятью программ. Сущность защиты ПЗУ заключается в предотвращении "дампинга" содержимого ПЗУ. Эта функция в более ранних версиях МК реализована путем запрета команд LDC, LDCI, LDE и LDEI. При таком подходе защищенная программа не могла использовать эти команды, что не разрешало программисту реализовывать эффективные алгоритмы с просмотром таблиц. В последних версиях МК использование функции защиты ПЗУ никаких ограничений на программирование не накладывает.

1.2.2.3. Стек

Стек МК Z8 может располагаться во внутреннем ОЗУ или во внешней памяти данных. Размещение стека программируется путем записи бита D2 в регистр режима портов 0 и 1 -P01M. Запись 0 в этот бит задает внешний стек, 1 -внутренний. Такой выбор возможен только для модели 40, имеющей интерфейс внешней памяти, для остальных моделей бит D2 должен быть установлен в 1.

Расположение верхушки стека задается шестнадцатибитным указателем стека, размещенным в регистрах SPH и SPL стандартного регистрового файла. Для всех моделей, кроме модели 40, достаточно восьмибитного указателя стека (т.к. объем внутреннего ОЗУ не превышает 256 байт), и он размещается в регистре SPL. Регистр SPH с адресом FEH используется при этом как регистр общего назначения GPR. Указатель стека декрементируется перед операцией загрузки и инкрементируется после операции извлечения. Его содержимое -это всегда адрес верхушки стека.

Стек МК Z8 -это стек возврата из подпрограмм и прерываний, а также стек данных. При работе МК возможно переполнение стека вниз и вверх. Ответственность за недопустимость переполнения лежит на разработчике программы, иначе результат будет непредсказуем.

1.2.3. Синхронизация

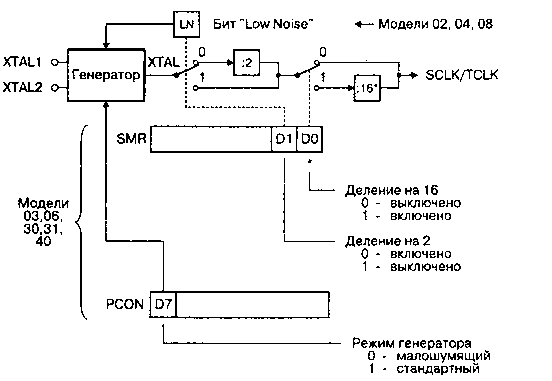

Обобщенная структурная схема синхронизации МК показана на рис 1.4.

Рис. 1.4 Структурная схема синхронизации

Схема состоит из задающего генератора, рассчитанного на подключение внешней времязадающей цепи или внешнего источника синхронизации, делителя частоты на 2 и делителя частоты на 16 (последний в моделях 02, 03, 04, 08 отсутствует). К входным контактам XTAL1 и XTAL2 (eXternal crysTAL) подключается времязадающая цепь, заставляющая генератор формировать синхроимпульсы с частотой XTAL. С выхода синхронизирующей схемы снимаются импульсы внутренней системной синхронизации SCLK (System CLocK) и синхронизации таймеров TCLK (Timer CLocK). Назначение делителя на 2 -формирование сигнала, а делитель на 16 предназначен для уменьшения рабочей частоты синхронизации и, соответственно, потребляемого тока, особенно в резервных режимах HALT и STOP.

Управление частотой в разных моделях МК осуществляется двумя способами. В моделях 02, 04, 08 управление сводится только к переводу схемы в малошумящий режим путем программирования (масочно или электрически) бита малошумящего режима Noise"(см. верхнюю часть рис.1.4.). При этом задающий генератор переводится в малошумящий режим и отключается делитель на 2. Максимальная частота работы генератора в этом режиме ограничивается 4 МГц и несколько снижается нагрузочная способность.

В моделях 03, 06, 30, 31 и 40 управление схемой синхронизации осуществляется путем записи управляющей информации в регистры PCON и SMR в процессе выполнения прикладной программы МК (см. нижнюю часть рис 1.4). Бит D7 регистра PCON управляет режимом задающего генератора, а биты D1 и D0 регистра SMR -делителями на 2 и на 16 соответственно. Логика управления показана на схеме.

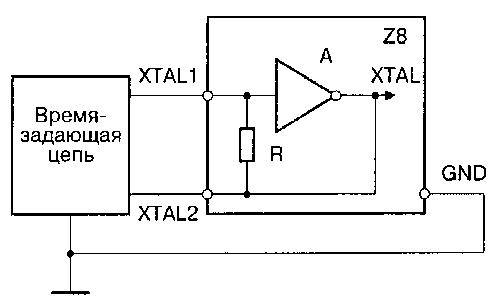

Схема задающего генератора показана на рис 1.5. Генератор построен на основе инвертирующего усилителя постоянного тока A с выполненной внутри кристалла резистивной обратной связью R. Схема генератора рассчитана на подключение внешней времязадающей цепи, являющейся гибкой обратной связью усилителя.

Рис. 1.5 Схема задающего генератора

Для устойчивого самовозбуждения генератора необходимо соблюдение условий баланса амплитуд и баланса фаз на частоте генерации. Условие баланса амплитуд заключается в равенстве 1 произведения коэффициента усиления усилителя на коэффициент передачи цепи обратной связи. Условие баланса фаз требует, чтобы суммарный сдвиг фаз в схеме был равен 0 (360о). Поскольку инвертирующий усилитель дает сдвиг фазы 180о, то цепь обратной связи должна обеспечивать фазовый сдвиг также на 180о.

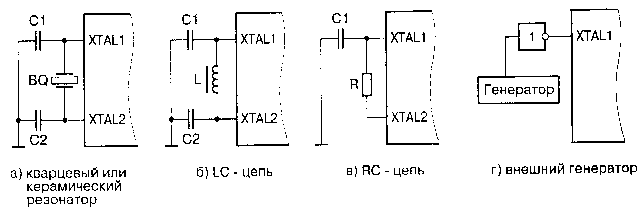

Этим условиям удовлетворяют схемы времязадающих цепей, показанные на рис.1.6. Генератор может работать с кварцевым или керамическим резонатором, LC -цепью, RC -цепью и внешним генератором. Работа генератора с RC -цепью требует определенной реконфигурации внутренней схемы, что достигается программированием (масочно или электрически) специального бита RC. Такую возможность имеют модели 03, 06, 30, 31, 40. Что касается моделей 02, 04, 08, то возможность запуска от RC - цепи имеют только самые последние версии этих моделей. Устойчивое возбуждение генератора возможно на частотах от 10 КГц до максимальной (см. табл.1.1.).

Рис. 1.6 Времязадающие цепи генератора

1.2.4. Сброс и сторожевой таймер

Функция сброса (Reset) необходима для инициализации важнейших элементов МК: схемы управления и синхронизации, программного счетчика (он устанавливается в состояние 000СН), управляющих регистров и портов (для определения их состояния после сброса для разных моделей МК, см. приложение 1).

Функция сброса активируется в следующих случаях:

- при подаче низкого уровня на вход /RESET (только для модели 40);

- при включении питания VСС;

- при переполнении сторожевого таймера WDT;

- при восстановлении из режима STOP.

В последнем случае (так называемый "теплый" старт) и в случае переполнения сторожевого таймера в режиме STOP порты и управляющие регистры не реинициализируются.

Функция сброса используется также для защиты памяти МК от падения напряжения питания. Это обеспечивается включением функции сброса при падении питающего напряжения VСС ниже порога защиты VLV (Low Voltage) -2-.6 В. Если уровень напряжения не снизится ниже уровня работоспособности КМОП-логики VCMOS (1.2 В), то возможно сохранение содержимого памяти МК и продолжение нормальной работы после восстановления VСС и автосброса. Это позволяет защитить МК от кратковременных "провалов" питающего напряжения.

Пока сброс активен, на выход /AS подаются импульсы внутренней синхронизации, выход /DS имеет низкий потенциал, R//W -высокий.

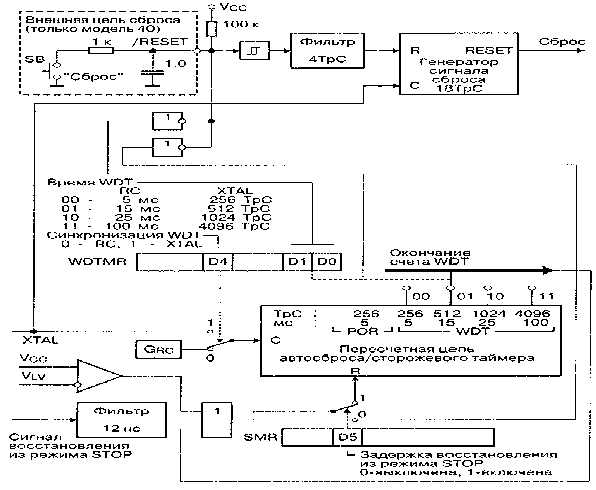

Обобщенная структурная схема сброса и сторожевого таймера показана на рис. 1.7.

Рис. 1.7. Схема сброса/сторожевого таймера

Схема содержит генератор сигнала внутреннего сброса, синхронизируемого импульсами основного генератора XTAL. Этот генератор обеспечивает минимальную длительность сигнала сброса 18 периодов TpC частоты XTAL. Запуск генератора осуществляется через фильтр длительности в 4 TpC. Иначе говоря, если длительность запускающего сигнала будет меньше 4 TpC, то сброса не произойдет. Если запускающий сигнал длиннее 18 TpC, то сброс будет удерживаться на время этого сигнала плюс 18 TpC.

Объединение сигналов запуска сброса осуществляется по схеме "монтажное ИЛИ", поэтому к внешнему выводу МК /RESET (только для модели 40) можно подключать схемы с выходными каскадами с открытым стоком. Для сброса МК с помощью кнопки SB "Сброс" следует применять внешнюю RC-цепь, показанную на том же рисунке. Для возможности использования RC-цепи вход запуска дополнен триггером Шмитта.

Таймер автосброса POR (Power-On Reset) и сторожевой таймер WDT (Watch-Dog Timer) выполнены в виде пересчетной цепи, которая, в общем случае, синхронизируется от дополнительного RC-генератора GRC или от основного генератора XTAL. Таймер POR имеет для всех моделей постоянное время, а таймер WDT -программируемое (за исключением моделей 02, 03, 04 и 08).

Запуск таймера автосброса POR осуществляется в следующих случаях:

- если уровень VСС поднимается выше уровня VLV;

- если становится активным сигнал восстановления из режима STOP;

- если имеет место окончание счета сторожевого таймера WDT.

В первом случае сигнал запуска вырабатывается специальным компаратором А. Во втором случае паразитные всплески сигнала источника подавляются фильтром 12 нс.

Во всех этих случаях происходит запуск таймера автосброса POR, время задержки которого гарантирует окончание переходных процессов в цепи питания VСС и выход на нормальный режим основного генератора синхронизации XTAL, после чего корректно выполняется внутренний сброс МК.

При восстановлении из режима STOP в случае применения LCили RC-времязадающих цепей основного генератора (см. п.1.2.3) нет необходимости выдерживать задержку автосброса, т.к. эти конфигурации генератора имеют малое время установления. Для сокращения задержки восстановления из режима STOP в этом случае сигнал от источника может быть подан непосредственно на вход запуска генератора сигнала сброса. При этом необходимо, чтобы сигнал от источника восстановления имел длительность не менее 4 TpC.

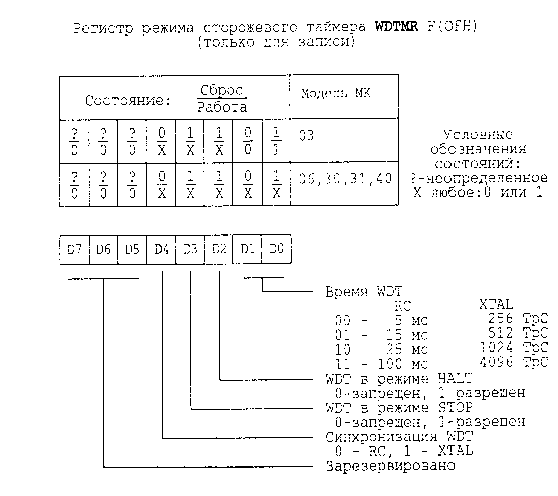

В МК, имеющих расширенную группу регистров F (модели 03, 06, 30, 31, 40), управление схемой сброса / сторожевого таймера осуществляется с помощью регистров режима сторожевого таймера WDTMR (Watch-Dog Timer Mode Register) и режима восстановления из режима STOP-SMR (STOP-Mode Recovery Register). Логика управления понятна из рисунка. Следует отметить, что поскольку генератор основной синхронизации выключается в режиме STOP, прежде чем перейти в этот режим необходимо, чтобы бит D4 WDTMR был установлен в состояние 0. Необходимо помнить, что регистр WDTMR доступен для записи только в течение первых 64 тактов (128 TpC) процессора после сброса, вызванного любым источником. Назначение разрядов регистра WDTMR полностью показано на рис. 1.8.

Рис. 1.8. Регистр WDTMR

Запуск и обновление сторожевого таймера осуществляется специальной командой WDT в рабочем режиме выполнения программы RUN. После однократного выполнения этой команды сторожевой таймер постоянно разрешен. Поэтому программа МК должна предусматривать периодическое повторение (с периодом, меньшим установленного времени сторожевого таймера) команды WDT. Это должно быть обеспечено программистом. В этом случае, при нормальной работе процессора сторожевой таймер будет периодически перезапускаться и не достигнет состояния окончания счета. При "зависании" процессора сторожевой таймер достигает состояния окончания счета, что вызывает запуск автосброса МК и выполнение программы с начала. Работа WDT в режимах HALT и STOP разрешается путем программирования соответствующих битов D2 и D3 регистра WDTMR. В этом случае, при переходе в соответствующий режим, WDT продолжает свою работу.

В модели 03 сторожевой таймер имеет фиксированную задержку 15 мс (при синхронизации от GRC) или 512TpC (при синхронизации от XTAL), а состояние битов D1 и D0 регистра WDTMR должно быть 01.

В моделях 02, 04, 08 регистры WDTMR и SMR отсутствуют, поэтому схема имеет фиксированную конфигурацию (соответствует изображенным на рис.1.7 положениям переключателей). Разрешение работы сторожевого таймера в режиме HALT осуществляется исполнением специальной команды WDH (выполняется до перехода в режим HALT). В режиме STOP в этих МК работа сторожевого таймера запрещена.

Запрещение работы сторожевого таймера во всех моделях МК происходит при выполнении внутреннего сброса. Исключение составляют некоторые модели (или отдельные модификации) имеющие программируемый (масочно или однократно) бит постоянного разрешения WDT (Permanent WDT). Если этот бит запрограммирован, то WDT постоянно разрешен и запрещение работы его после сброса не происходит.

Таким образом, функция сброса и сторожевой таймер обеспечивают корректный начальный запуск программы и перезапуск в случае сбоя программы.

1.2.5. Порты ввода/вывода

МК Z8 имеет до 32 линий ввода/вывода, сгруппированных в четыре восьмибитных порта Р0, Р1, Р2, Р3 (физическое наличие соответствующих выводов портов для каждой модели МК указано в табл.1.2). Порты размещены в адресном пространстве регистрового файла по адресам соответственно 00H, 01H, 02H, 03H.

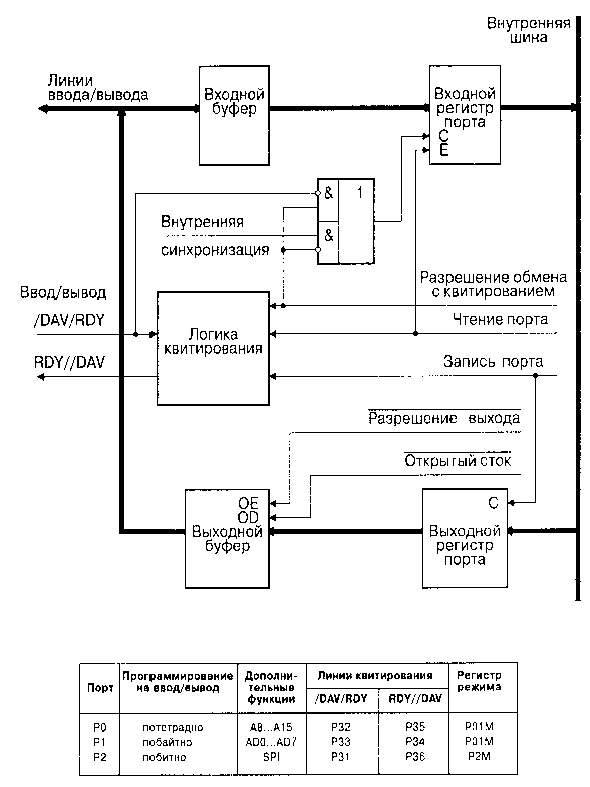

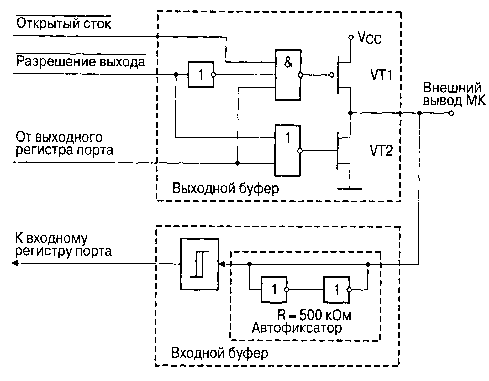

Порты Р0, Р1 и Р2 построены по типовой структуре, показанной на рис. 1.9. Каждый порт имеет входной и выходной регистры, входной и выходной буферы. Выходные буферы -двухтактные, однако, могут программироваться как схемы с открытым стоком (Open Drain). Кроме того, выходные буферы могут быть переведены в малошумящий режим.

Рис. 1.9. Структурная схема портов P0, P1 и P2

Работа линий портов может программироваться на ввод или вывод: Р0 -потетрадно, Р1 -побайтно (т.е. целиком), а Р2 -побитно (см. табл. на рис. 1.9). Порты могут работать в режиме синхронного программного обмена, в режиме обмена с квитированием, в режиме стробируемого ввода/вывода.

При синхронном программном обмене ввод или вывод реализуется в момент исполнения команд чтения или записи регистра порта. При этом внешнее устройство должно быть постоянно готово к обмену.

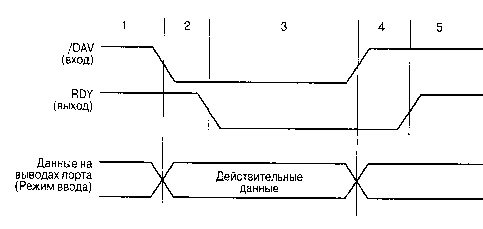

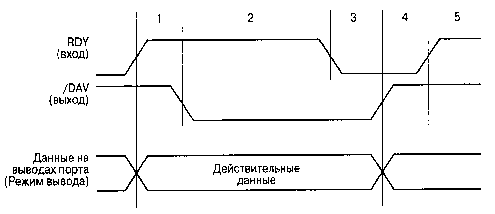

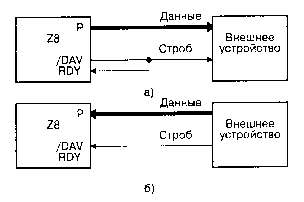

Режим обмена с квитированием или "рукопожатием" (Handshake) заключается в том, что МК и внешнее устройство обмениваются сигналами (квитанциями) ГОТОВНОСТИ к обмену -RDY (Ready) и ДЕЙСТВИТЕЛЬНОСТИ ДАННЫХ -/DAV (Data is Available). Ввод и вывод с квитированием подробно поясняются временными диаграммами, рис.1.10 и 1.11.

| Состояние 1. |

Сигнал RDY имеет высокий уровень, что указывает MK принять данные. |

| Состояние 2. |

Внешнее устройство помещает данные на выводы порта и активизирует сигнал /DAV. Это приводит к фиксации данных во входном регистре порта МК и генерирования запроса прерывания. |

| Состояние 3. |

МК переводит выход RDY в низкое состояние, сигнализируя внешнему устройству, что данные зафиксированы. |

| Состояние 4. |

Внешнее устройство возвращает линию /DAV в высокое состояние после получения низкого уровня сигнала RDY. |

| Состояние 5. |

МК должен среагировать на запрос прерывания и прочитать содержимое порта для завершения последовательности квитирования. На линии RDY устанавливается высокий уровень тогда и только тогда, когда порт уже прочитан и /DAV имеет высокий уровень. Это возврощает интерфейс в его начальное значение. |

Рис. 1.10. Ввод с квитированием

| Состояние 1. |

Вход RDY имеет высокий уровень, что указывает на готовность внешнего устройства к приему данных. |

| Состояние 2. |

МК записывает данные в регистр порта для инициализации передач данных. Запись в порт новых данных и переход выхода /DAV в состояние низкого уровня происходит только тогда, когда RDY имеет высокий уровень. |

| Состояние 3. |

Внешнее устройство делает уровень сигнала RDY низким после фиксации данных. Низкий уровень RDY вызывает генерирование запроса прерывания. МК может уже записать новые данные в ответ на низкий уровень DRY, однако эти данные не выводятся до состояния 5. |

| Состояние 4. |

Уровень выхода /DAV МК становится высоким в ответ на переход выхода RDY в состояние низкого уровня. |

| Состояние 5. |

Уровень выхода /DAV остается высоким, внешнее устройство может установить высокий уровень RDY, что возвращает интерфейс в его начальное состояние. |

Рис. 1.11. Вывод с квитированием

Для приема и передачи сигналов квитирования используются соответствующие линии ввода/вывода порта Р3 (см. табл. на рис.1.9). Выбор направления обмена с квитированием осуществляется в соответствии с направлением, запрограммированным для старшей тетрады порта Р0 и для старшего бита порта Р2.

Режим стробируемого ввода/вывода реализуется как частный случай обмена с квитированием по схеме рис. 1.12.

Рис. 1.12. Стробируемый ввод/вывод

а) вывод; б) ввод.

Дополнительно к основным функциям порты P0 и P1 могут использоваться для интерфейса внешней памяти (Р0 -старшие разряды адреса A8...A15, P1 -мультиплексированная шина адреса/данных AD0...AD7), а порт P2 -для последовательного интерфейса SPI в модели 06 (P20 -вход DI, P27 -выход D0).

Схемотехника портов P0, P1, P2 поясняется рис. 1.13. Двухтактный буферный выходной усилитель выполнен на комплементарных МОП-транзисторах VT1 и VT2. Отключение транзистора VT1 переводит буферный усилитель в конфигурацию с открытым стоком. Входной буфер содержит автофиксатор и триггер Шмитта, который обеспечивает формирование входного сигнала.

Рис. 1.13. Схемотехника входного и выходного буферов

Автофиксатор предназначен для фиксации потенциала незадействованного входа на уровне допустимых КМОП потенциалов, близких к потенциалам шины питания VCC или общей шины GND. Этим исключается переход пары входных транзисторов в активный режим и резкое возрастание потребляемого тока. Автофиксатор представляет собой бистабильную ячейку (триггер), выполненную на двух замкнутых в кольцо инверторах, управляемую по выходу. Шунтирующее сопротивление автофиксатора -не менее 500 кОм. В ряде случаев, когда входы задействованы, шунтирующее действие автофиксатора нежелательно. Поэтому в некоторых модификациях МК предусмотрен специальный бит отключения автофиксаторов (Z86C30/31/40).

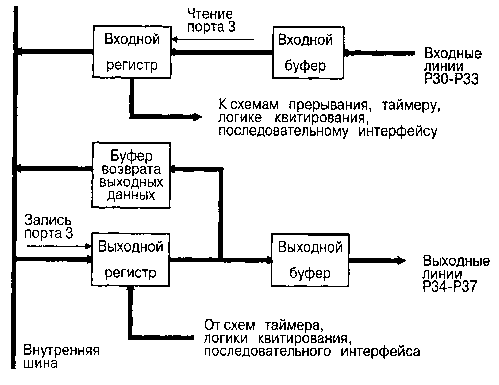

Порт Р3 -особый. Первые четыре его линии P30...P33 предназначены для ввода, вторые -P34...P37 -для вывода. Структурная схема порта и таблица назначения его выводов в различных режимах приведены на рис. 1.14. Независимо от выбранного режима с входами порта P3 связаны соответствующие запросы прерывания, указанные в таблице. Физическое наличие выводов порта P3 для разных моделей МК см. в табл. 1.2.

Рис. 1.14. Структурная схема порта P3

| Вывод P3 |

Аналоговый режим |

Квитирование |

SPI |

Таймеры |

Внешняя память |

Прерывания |

| P30 |

IRQ3 |

| P31 |

AN1 |

/DAV2/RDY2 |

TIN |

IRQ2 |

| P32 |

AN2 |

/DAV0/RDY0 |

IRQ0 |

| P33 |

REF |

/DAV1/RDY1 |

IRQ1 |

| P34 |

AN1-OUT |

RDY1/DAV1 |

SK |

/DM |

| P35 |

AN2-OUT* |

RDY0/DAV0 |

/SS |

| P36 |

RDY2/DAV2 |

TOUT |

| P37 |

AN2-OUT |

Примечание:

*только для моделей 03 и 06.

Порт P3 содержит четырехбитные входной и выходной регистры, входной и выходной буферы. Наличие четырехбитного буфера возврата позволяет при чтении порта P3 контролировать данные на выходных линиях. Запись информации в младшую тетраду порта P3 не имеет эффекта.

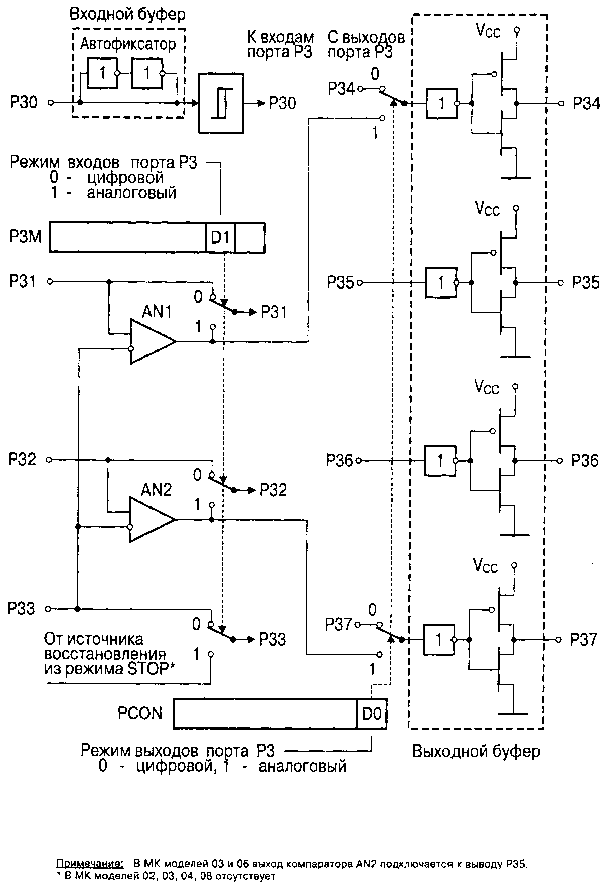

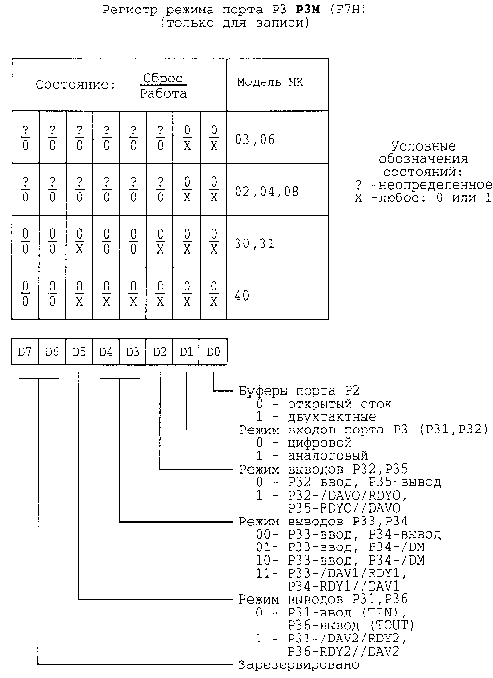

Схемотехника порта P3 иллюстрируется рис. 1.15. Дополнительной особенностью МК является наличие двух встроенных аналоговых компараторов AN1 и AN2, позволяющих решать вопросы сравнения аналоговых сигналов, квантования сигналов, аналого-цифрового преобразования. Входы и выходы порта P3 используются для обслуживания аналоговой схемы. Переключение входов в аналоговый режим осуществляется битом D1 регистра режима порта 3 PЗM, а выходов -битом D0 регистра управления портами PCON. Входы P31 и P32 используются соответственно для неинвертирующих входов компараторов, а вход P33 является входом опорного напряжения REF, общего для AN1 и AN2.

Рис. 1.15. Схемотехника порта P3

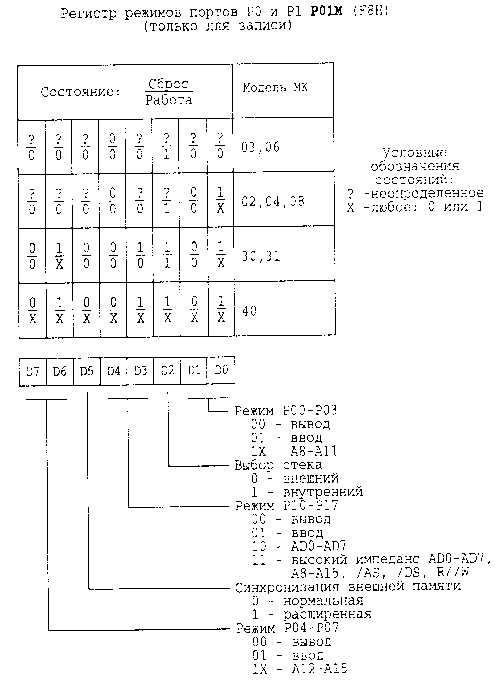

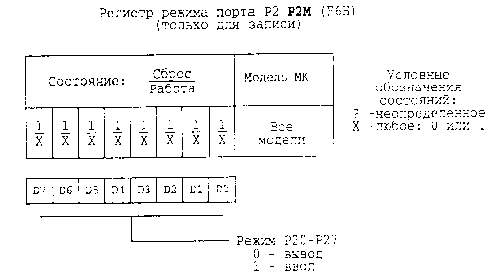

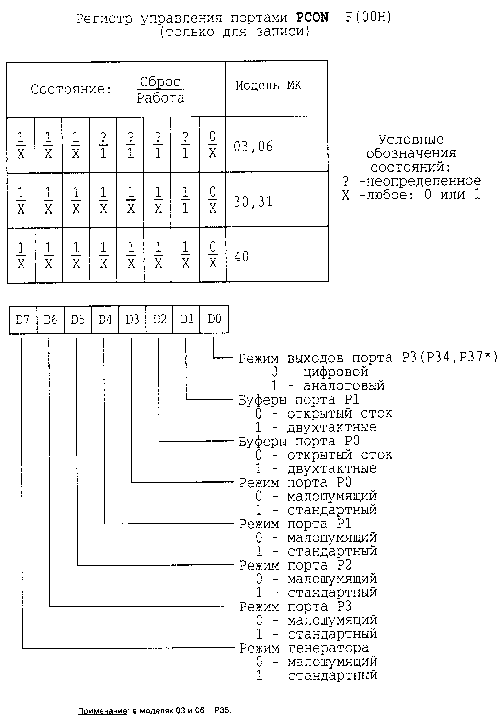

Управление работой портов реализуется путем записи информации в управляющие регистры: регистр режимов портов P0 и P1 -P01M, регистр режима порта P2 -P2M, регистр режима порта P3 -P3M. Все эти регистры находятся в рабочей группе F стандартного РФ. В моделях 03, 06, 30, 31 и 40, кроме того, для управления режимами работы выходных буферов портов (режим "открытый сток" и малошумящий режим) задействован регистр управления портами PCON, расположенный в расширенной группе регистров F. Все эти регистры предназначены только для записи. Результат чтения этих регистров будет равен FFH.

Назначение разрядов этих регистров и их состояние после сброса МК для разных моделей МК поясняется рис. 1.16 -1.19.

Рис. 1.16. Регистр режимов портов P0 и P1

Рис. 1.17. Регистр режима порта P2

Рис. 1.18. Регистр режима порта P3

Рис. 1.19. Регистр управления портами PCON

Разрабатывая прикладную программу МК, необходимо предусматривать в ней процедуру инициализации портов ввода/вывода до выполнения операций обмена данными с внешними устройствами.

1.2.6. Таймеры/счетчики

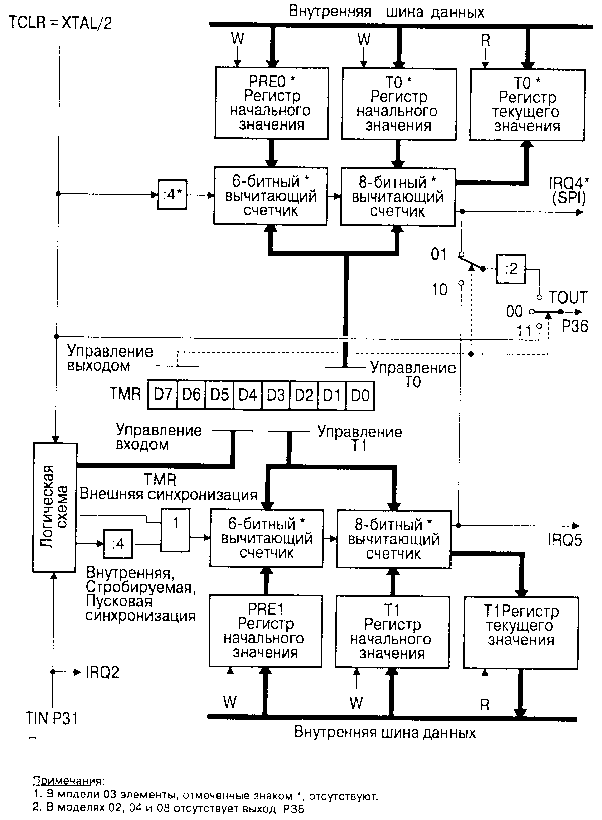

МК Z8 может иметь до двух таймеров/счетчиков, в зависимости от модели (см. табл.1.2). Каждый из 8-битных таймеров/счетчиков Т0 и Т1 снабжен 6-битным предделителем PRE0 и PRE1 (рис.1.20). Работа таймеров/счетчиков происходит независимо от работы процессора, что освобождает его от выполнения критичных временных операций, таких как счет событий, измерение временных интервалов, генерирование импульсов заданной длительности и т.п.

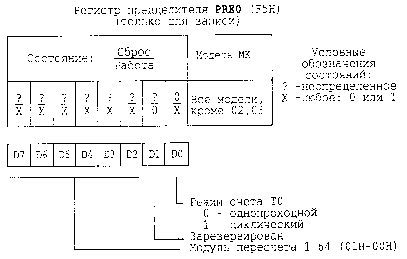

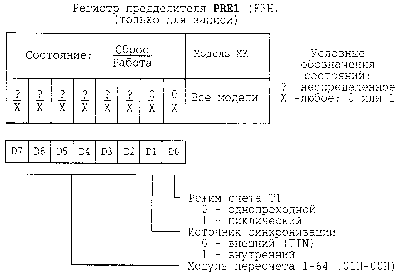

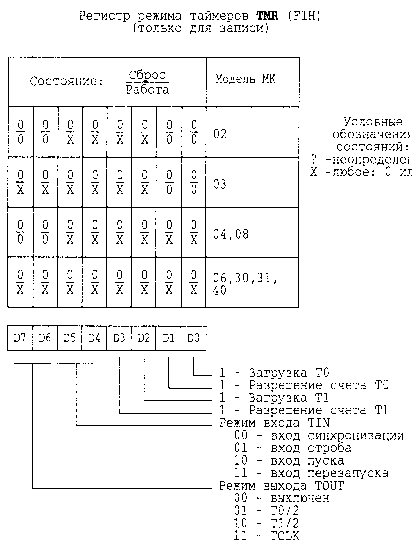

Рис. 1.20. Структурная схема таймеров/счетчиков

Каждый из таймеров/счетчиков может работать в однопроходном или циклическом режимах. В первом случае, при достижении таймером/счетчиком конца счета, счет прекращается, во втором —начальное значение перезагружается и счет продолжается. При управлении от внутренней синхронизации TCLK (TCLK = XTAL/2 в основном режиме работы генератора), ее частота дополнительно делится на 4. Этот делитель вместе с 6-битным предделителем и 8-битным таймером/счетчиком образуют синхронную 16-битную цепь. Таймер/счетчик T1 может также управляться с внешнего входа TIN, в качестве которого используется вывод Р31. Выходы таймеров/счетчиков и выход внутренней синхронизации могут быть с помощью программы скоммутированы на выход TOUT, в качестве которого используется вывод Р36. Управление работой таймеров/счетчиков осуществляется с помощью регистра режимов таймеров TMR. Регистры таймеров/счетчиков T0 и T1, предделителей PRE0 и PRE1, а также регистр TMR размещены в адресном пространстве СРФ, рабочая группа F ( см. рис.1.2). Поэтому для управления и контроля за работой таймеров/счетчиков никаких специальных команд не требуется. Каждый из предделителей PRE0 (F5H) и PRE1 (F3H) состоит из 8-битного регистра начального значения и 6-битного вычитающего счетчика (см. рис.1.20). Регистры предделителей предназначены только для записи, кроме начального значения содержат управляющие биты. Назначение разрядов этих регистров, их состояние после сброса и в процессе работы поясняется рис.1.21 и рис.1.22. Попытка чтения этих регистров дает результат FF. Начальное значение предделителей может быть в диапазоне от 1 до 64 ( 01H,...,3FH,00H ).

Каждый из таймеров/счетчиков (см. рис.1.20 ) T0 (F4H) иT1 (F2H) состоит из 8-битного вычитающего счетчика, регистра начального значения (только для записи) и регистра текущего значения (только для чтения). Начальное и текущее значения могут быть в диапазоне от 1 до 256 (01H,...,FFH,00H). После сброса состояние регистров T0 и T1 —неопределенное.

Рис. 1.21. Регистр предделителя PRE0

Рис. 1.22. Регистр предделителя PRE1

Регистр TMR содержит группы битов, управляющие загрузкой начальных значений, пуском/остановом таймеров, режимом входа TIN и режимом выхода TOUT. Назначение разрядов регистра TMR, состояние их после сброса и допустимые состояния в процессе работы для разных моделей МК показаны на рис.1.23.

Рис. 1.23. Регистр режимов таймеров TMR

Установка бита загрузки (D0 для T0 и D2 для T1) вызывает пересылку начального значения из регистров начального значения соответствующего предделителя и таймера в вычитающие счетчики. После загрузки эти управляющие биты сбрасываются. Новое значение может быть загружено в вычитающие счетчики в любое время. Если счетчики были запущены, то счет будет продолжаться с нового значения.

Таймеры/счетчики сохраняют свое состояние, пока бит разрешения счета (см. рис.1.23) равен 0. Для запуска таймеров/счетчиков соответствующий бит разрешения счета (D1 для T0 и D3 для T1) должен быть установлен в 1. Первый декремент будет иметь место через 4 периода внутренней синхронизации после установки программой бита разрешения счета или в следующем периоде внешней синхронизации (со входа TIN).

Биты загрузки и разрешения могут быть установлены одновременно. Например, с использованием команды

OR TMR,# 03H

можно загрузить и запустить таймер/счетчик T0.

1.2.7. Прерывания

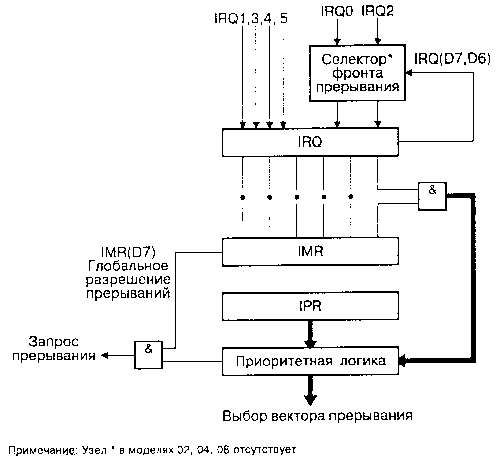

МК Z8 поддерживают 6-уровневую схему приоритетных прерываний от различных источников. Набор внешних источников прерывания связан со входами порта Р3 и инициирует запросы прерывания IRQ0,...,IRQ3 (см.табл. на рис.1.14). К внутренним источникам относятся таймеры/счетчики T0, T1 и последовательный интерфейс SPI. Им соответствуют запросы прерывания IRQ4, IRQ5. Обобщенная структурная схема организации прерываний и таблица соответствия источников показаны на рис.1.24. Следует отметить, что кроме аппаратной установки любой из запросов может бытьустановлен программным путем.

Аппаратные источники прерываний

| Запрос прерывания |

Модель МК |

| 02 |

03 |

06 |

04, 08 |

30, 31, 40 |

| IRQ0 |

P32 f |

P32 s |

P32 s |

P32 f |

P32 s |

| IRQ1 |

P33 f |

P33 f |

P33 f |

P33 f |

P33 f |

| IRQ2 |

P31 f |

P31 s |

P31 s |

P31 f |

P31 s |

| IRQ3 |

P32 f |

SPI |

P32 r |

P30 f |

| IRQ4 |

T0 |

T0 |

T0 |

| IRQ5 |

T1 |

T1 |

T1 |

T1 |

T1 |

Рис. 1.24. Структурная схема организации прерываний

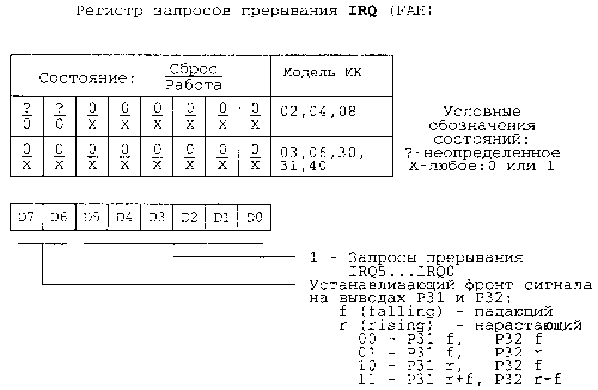

Схема управления прерываниями включает три управляющих регистра: регистр запросов прерывания IRQ, регистр маски прерывания IMR и регистр приоритетов прерывания IPR. Все регистры размещены в СРФ, рабочая группа F. Каждый внешний сигнал устанавливает в 1 соответствующий бит запроса в регистре IRQ (рис.1.25) при появлении фронта сигнала, указанного в таблице на рис.1.24. В моделях 03, 06, 30, 31 и 40 фронт сигнала, устанавливающий запросы IRQ0 и IRQ2, программируется путем записи информации в два старших бита регистра IRQ. Запросы прерываний от таймеров/счетчиков устанавливаются при достижении ими конца счета, а запрос от SPI —по завершении приема символа.

Рис. 1.25. Регистр запросов прерывания IRQ

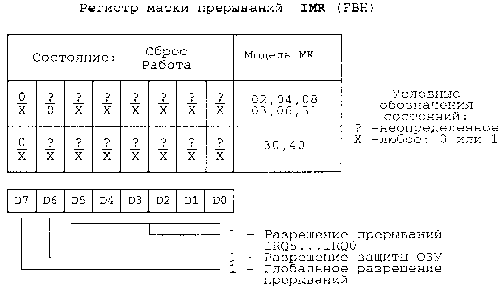

Регистр маски прерываний IMR (рис.1.26) позволяет маскировать как каждое прерывание IRQ5 —IRQ0 отдельно (биты D5-D0), так и все прерывания глобально (бит D7). Последний бит устанавливается и сбрасывается особыми командами разрешения и запрещения прерываний EI и DI. Он автоматически сбрасывается при вызове подпрограммы обслуживания прерывания и автоматически устанавливается при выполнении команды возврата из подпрограммы обслуживания прерывания IRET. Следует отметить, что перед изменением содержимого IMR или IPR бит D7 регистра IMR должен быть сброшен.

Рис. 1.26. Регистр маски прерываний IMR

Регистр приоритета прерываний IPR (рис.1.27) позволяет устанавливать любое соотношение приоритетов как между группами прерываний А, В, С, так и между отдельными запросами прерываний внутри группы. В каждую группу включено по два запроса.

МК Z8 поддерживает как процесс векторных прерываний, так и процесс поллинга.

Рис. 1.27. Регистр приоритетов прерываний IMR

В случае векторного процесса каждый уровень прерывания имеет собственный вектор —адрес подпрограммы обслуживания этого уровня прерывания. Векторы прерываний размещены в начальной зоне ПЗУ (см. рис. 1.3). Инициализация процесса векторного прерывания происходит, если прерывания глобально разрешены и есть хотя бы один незамаскированный запрос прерывания. Если таких запросов несколько, то выбирается вектор прерывания с наивысшим приоритетом. Далее реализуется следующая последовательность действий:

— загружается в стек младший байт PC;

— загружается в стек старший байт PC;

—загружается в стек регистр флагов FLAGS;

— читается старший байт вектора;

— читается младший байт вектора;

—вектор загружается в PC.

Эта последовательность занимает 24 такта синхронизации TpC. Наихудшее время реакции на прерывание можно вычислить, прибавив к этому времени 2TpC для синхронизации внешнего запроса прерывания и время выполнения самой длинной команды в прерываемой программе.

1.3. Система команд микроконтроллеров Z8

Математические возможности МК характеризуются системой команд. В МК использован двухадресный принцип построения команд, что позволяет сократить количество требуемых пересылок операндов. Первый операнд после выполнения команды становится результатом и называется операндом-получателем ( Destination Operand ), а второй —сохраняет свое значение и называется операндом-источником ( Source Operand ). Первый в описании системы команд обозначен аббревиатурой dst, а второй —src.

Код любой команды МК содержит код операции (КОП), определяющий операцию команды, и до двух адресных полей. Способы трактовки кодов в адресном поле называются способами адресации операндов.Прежде чем рассматривать набор команд, необходимо более подробно рассмотреть используемые способы адресации операндов.

1.3.1. Способы адресации операндов

В МК Z8 использовано шесть основных способов адресации операндов :

— регистровая ( Register );

— косвенная регистровая ( Indirect Register );

— индексная ( Indexed );

— прямая ( Direct );

— относительная ( Relative );

— непосредственная ( Immediate ).

Кроме того, регистровая и косвенная регистровая адресации имеют ряд модификаций: они могут использовать сокращенный 4-битный адрес рабочего регистра, полный 8-битный адрес регистра, сокращенный 4-битный адрес рабочей пары регистров, полный 8-битный адрес регистровой пары. При адресации пар регистров используется четное выравнивание, т.е. допустимые адреса —четные числа. Шестнадцатибитные операнды занимают в регистровом файле пару регистров, причем по четному адресу размещается старший байт.

Все способы адресации операндов в системе команд МК Z8 приведены в табл.1.7. В таблице указаны условные обозначения способов адресации, используемые в дальнейшем в таблице команд, наименование способа адресации, обозначение операнда на языке ассемблера, диапазон значений адреса и номер рисунка, на котором дана графическая интерпретация способа адресации.

Следует отметить, что адреса типа R, RR, IR, IRR предполагают использование как полного 8-битного адреса регистра, так и сокращенного 4-битного. В последнем случае адрес размещается в младшей тетраде адресного байта, а в старшей тетраде указывается код 1110B (EH) :

Поэтому обращение к регистрам рабочей группы E СРФ возможно только с помощью рабочей регистровой адресации (см. п.п.1.2.2.1).

Таблица 1.7. Способы адресации операндов

| Способ |

Наименование |

Операнд |

Диапазон |

Рис. |

| r |

Рабочая регистровая(РР) |

Rn |

n=0,...,15 |

1.35 |

| R |

Регистровая или РР |

Reg

Rn

|

00H —FFH

n=0,...,15

|

1.36

1.35

|

| RR |

Регистровая пара или PP пара (четное выравнивание) |

Reg

RRp

|

00H —FEH

p=0,...,14

|

1.38

1.37

|

| Ir |

Косвенная РР |

@Rn |

n=0,...,15 |

1.39 |

| IR |

Косвенная регистровая или косвенная РР |

@Reg

@Rn

|

00H —FFH

n=0,...,15

|

1.40

1.39

|

| Irr |

Косвенная через РР пару |

@RRp |

p=0,...,14 |

1.41 |

| IRR |

Косвенная через регистровую пару или РР пару |

@Reg

@RRp

|

00H —FEH

p=0,...,14

|

1.42

1.41

|

| X |

Индексная |

Reg(Rn) |

00H —FFH |

1.43 |

| DA |

Прямая |

Addrs |

0H —FFFFH |

1.44 |

| RA |

Относительная |

Addr |

-128- +127 |

1.45 |

| IM |

Непосредственная |

#Data |

00H —FFH |

1.46 |

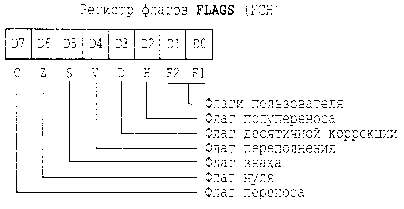

1.3.2. Флаги процессора

Флаговый регистр FLAGS (FCH) содержит информацию о текущем состоянии процессора. Флаги и их расположение в регистре приведены на рис.1.47. Состояние флагового регистра после сброса является неопределенным.

Рис. 1.47. Регистр флагов FLAGS

Флаговый регистр FLAGS содержит 6 флагов состояния, информация в которых устанавливается в результате работы процессора. Четыре флага (C, V, Z, S) используются командами условного перехода. Два флага (H и D) используются командой десятичной коррекции. Оставшиеся два бита могут быть использованы как флаги пользователя (F1 и F2). Ниже подробно рассмотрено назначение каждого из основных флагов МК Z8.

1.3.2.1. Флаг переноса C (Carry Flag)

Флаг переноса устанавливается в 1, если в результате арифметической операции генерируется “перенос из” или “заем в” старший 7-ой бит результата. В противном случае флаг С очищается в 0.

В процессе выполнения команд циклического или арифметического сдвига флаг переноса С содержит последний бит, выдвинутый из указанного в команде регистра.

Команды могут устанавливать, сбрасывать или инвертировать (дополнять) флаг переноса.

1.3.2.2. Флаг нуля Z (Zero Flag)

Если в результате арифметической или логической операции получается нулевой результат, то флаг Z устанавливается в 1, в противном случае флаг Z очищается в 0.

Если результат команды проверки бита в регистре равен 00Н,0то флаг нуля устанавливается в 1, в противном случае — очищается в 0.

Если результат выполнения команды циклического или арифметического сдвига равен 00Н, флаг Z устанавливается в 1, иначе —сбрасывается в 0.

1.3.2.3. Флаг знака S (Sign Flag)

Флаг знака хранит значение старшего бита результата текущей арифметической или логической операции, операции циклического илиарифметического сдвига.

Для производства арифметических операций над числами со знаком в МК используется представление информации в дополнительном коде. Положительное число при этом идентифицируется в старшем значащем разряде и, соответственно, значение флага знака также равно 0. Отрицательное число идентифицируется 1 в старшем значащем разряде и, соответственно, флаг S также будет равен 1.

1.3.2.4. Флаг переполнения V (Overflow Flag)

Для знаковых арифметических операций, операций циклического и арифметического сдвигов флаг переполнения V устанавливается в 1, если результат больше максимально возможного положительного числа (+127) или меньше минимально возможного отрицательного числа (-128), представленного 8-битным дополнительным кодом. Флаг V устанавливается в 0, если переполнение отсутствует. В результате поразрядных логических операций флаг V всегда сбрасывается в 0.

1.3.2.5. Флаг десятичной коррекции D (Decimal Adjust Flag)

Флаг десятичной коррекции D используется для двоично-десятичной арифметики BCD (Binary Coded Decimal). Поскольку алгоритм десятичной коррекции различен для сложения и вычитания, этот флаг сохраняет информацию о последней выполненной команде, для последующей команды десятичной коррекции DA. После выполнения операциивычитания флаг D устанавливается в 1, а после операции сложения —очищается в 0.

1.3.2.6. Флаг полупереноса H (Half Carry Flag)

Флаг полупереноса H устанавливается в 1, когда при сложениичисел генерируется перенос из 3-его бита или при вычитании генерируется заем в 3-ий бит. Флаг H используется командой десятичной коррекции DA.

Значения всех флагов изменяются командой IRET при восстановлении из стека состояния флагового регистра. Команды WDH и WDT устанавливают флаги Z, S и V в неопределенное состояние. Команда SWAP устанавливает в неопределенное состояние флаги C и V.

1.3.3. Набор команд

Команды микроконтроллеров Z8 функционально могут быть разделены на восемь групп:

— команды загрузки;

— арифметические команды;

— логические команды;

— команды управления программой;

— команды манипуляции битами;

— команды пересылки блоков;

— команды сдвигов;

— команды управления процессором.

1.3.3.1. Описание системы команд

В табл.1.8 приведено краткое описание системы команд микроконтроллеров, причем для каждой команды дано мнемоническое обозначение, принятое в языке ассемблера, указан состав операндов и смысл команды на английском языке ( для понимания происхождения мнемоники как аббревиатуры ) и на русском языке. Аббревиатура “сс” в колонке операндов команд управления программой означает код условия ( condition ), а аббревиатура “r”— любой регистр из рабочей группы ( register ).

Таблица 1.8. Краткое описание системы команд микроконтроллера Z8

| Мнемоника |

Операнды |

Наименование команды |

| Английский язык |

Русский язык |

| КОМАНДЫ ЗАГРУЗКИ |

CLR

LD

LDC

LDE

POP

PUSH

|

dst

dst,src

dst,src

dst,src

dst

src

|

Clear

Load

Load Constant

Load External Data

Pop

Push

|

Очистить

Загрузить

Загрузить константу

Загрузить внешние данные

Извлечь из стека

Загрузить в стек

|

| АРИФМЕТИЧЕСКИЕ КОМАНДЫ |

ADC

ADD

CP

DA

DEC

DECW

INC

INCW

SBC

SUB

|

dst,src

dst,src

dst,src

dst

dst

dst

dst

dst

dst,src

dst,src

|

Add with Carry

Add

Compare

Decimal Adjust

Decrement

Decrement Word

Increment

Increment Word

Subtract with Carry

Subtract

|

Сложить с переносом

Сложить

Сравнить

Десятичная коррекция

Декремент

Декремент слова

Инкремент

Инкремент слова

Вычесть с заемом

Вычесть

|

| ЛОГИЧЕСКИЕ КОМАНДЫ |

AND

COM

OR

XOR

|

dst,src

dst

dst,src

dst,src

|

Logical AND

Complement

Logical OR

Logical EXCLUSIVE OR

|

Логическое И

Дополнение ( НЕ )

Логическое ИЛИ

Исключающее ИЛИ

|

| КОМАНДЫ УПРАВЛЕНИЯ ПРОГРАММОЙ |

CALL

DJNZ

IRET

JP

JR

RET

|

dst

r,dst

cc,dst

cc,dst

|

Call Procedure

Decrement and Jump

Non Zero

Interrupt Return

Jump

Jump Relative

Return

|

Вызов подпрограммы

Декремент и переход,

если не нуль

Возврат из прерывания

Переход

Переход относительный

Возврат из подпрограммы

|

| КОМАНДЫ МАНИПУЛЯЦИИ БИТАМИ |

TCM

TM

AND

OR

XOR

|

dst,src

dst,src

dst,src

dst,src

dst,src

|

Test Complement

Under Mask

Test Under Mask

Bit Clear

Bit Set

Bit Complement

|

Проверить дополнение

с маской

Проверить с маской

Очистить биты

Установить биты

Дополнить биты

|

| КОМАНДЫ ПЕРЕСЫЛКИ БЛОКОВ |

LDCI

LDEI

|

dst,src

dst,src

|

Load Constant

Autoincrement

Load External Data

Autoincrement

|

Загрузить константу

с автоинкрементом

Загрузить внешние данные

с автоинкрементом

|

| КОМАНДЫ СДВИГОВ |

RL

RLC

RR

RRC

SRA

SWAP

|

dst

dst

dst

dst

dst

dst

|

Rotate Left

Rotate Left

Through Carry

Rotate Right

Rotate Right

Through Carry

Shift Right Arithmetic

Swap Nibbles

|

Циклический влево

Циклический влево

через перенос

Циклический вправо

Циклический вправо

через перенос

Арифметический вправо

Свопинг полубайтов

|

| КОМАНДЫ УПРАВЛЕНИЯ ПРОЦЕССОРОМ |

CCF

DI

EI

HALT

NOP

RCF

SCF

SRP

STOP

WDH

WDT

|

src

|

Complement Carry Flag Disable Interrupts

Enable Interrupts

Halt

No Operation

Reset Carry Flag

Set Carry Flag

Set Register

Pointer

Stop

WDT Enable During

HALT

WDT Enable or Refresh

|

Дополнить флаг переноса

Запретить прерывания

Разрешить прерывания

Переход в режим HALT

Нет операции

Сбросить флаг переноса

Установить флаг переноса

Установить указатель

регистров

Переход в режим STOP

Разрешение сторожевого

таймера в режиме HALT

Разрешение или переза-

пись сторожевого таймера

|

1.3.3.2. Условия ветвления программы

Команды переходов JP и JR обеспечивают ветвление программы по различным условиям. В качестве условий используются состояния флагов C,Z,S и V, а также их логические функции. Набор допустимых для языка ассемблера условий с указанием мнемонического обозначения (cc), значения, соответствующего состояния флагов и шестнадцатеричного кода условия приведен в табл.1.9. Набор условий предусматривает ветвление по состояниям отдельных флагов, а также по всем возможным соотношениям между целыми числами со знаком и между беззнаковыми целыми числами.

Таблица 1.9. Мнемоника условий (cc) и цифра КОП (c)

| cc |

Значение |

Состояние флагов |

c |

| F |

Всегда ложно |

— |

0 |

| Всегда истинно |

— |

8 |

| C |

Есть перенос |

C=1 |

7 |

| NC |

Нет переноса |

C=0 |

F |

| Z |

Есть нуль |

Z=1 |

6 |

| NZ |

Нет нуля |

Z=0 |

E |

| PL |

Положительно |

S=0 |

D |

| MI |

Отрицательно |

S=1 |

5 |

| OV |

Переполнение |

V=1 |

4 |

| NOV |

Нет переполнения |

V=0 |

C |

| EQ |

Равно |

Z=1 |

6 |

| NE |

Не равно |

Z=0 |

E |

| GE |

Больше или равно |

(S xor V)=0 |

9 |

| LT |

Меньше |

(S xor V)=1 |

1 |

| GT |

Больше |

(Z or (S xor V))=0 |

A |

| LE |

Меньше или равно |

(Z or (S xor V))=1 |

2 |

| UGE |

Б/з больше или равно |

C=0 |

F |

| ULT |

Б/з меньше |

C=1 |

7 |

| UGT |

Б/з больше |

(C=0 and Z=0)=1 |

B |

| ULE |

Б/з меньше или равно |

(C or Z)=1 |

3 |

1.4. Конструктивное исполнение микроконтроллеров Z8

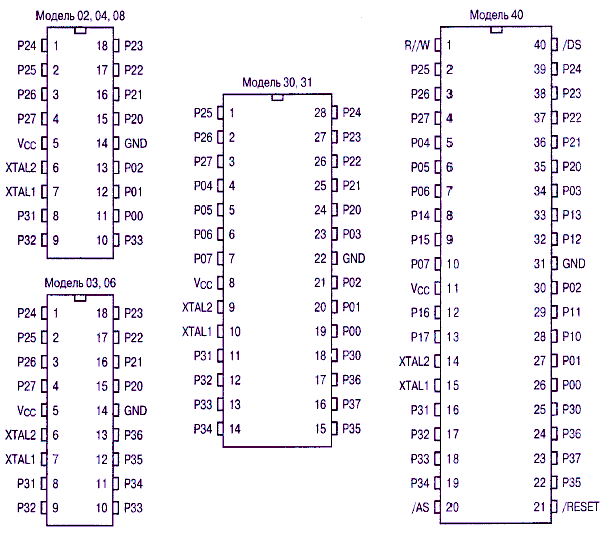

Микроконтроллеры широкого применения Z8 выпускаются в различном конструктивном исполнении. Наиболее дешевым и удобным для большинства применений является корпус типа DIP ( Dual In Line Package ). Схема расположения выводов МК для корпусов этого типа показана на рис.1.48.

Большинство моделей МК имеет также вариант исполнения в корпусе типа SOIC ( Smal Outline Package ), предназначенном для монтажа на поверхность. Модель 40 выпускается также и в квадратных 44 выводных корпусах типа PLCC ( Plastic Chip Carrier ) и QFP (Quad Flat Pack ). Модели МК 30, 31, и 40 с возможностью многократного перепрограммирования производятся в корпусах типа CerDIP Window Lid, имеющих кварцевое окно для оптического стирания.

Полное обозначение микросхемы, кроме шифра, указанного в табл.1.1, содержит дополнительно две цифры, соответствующие максимальной частоте в мегагерцах, три буквы и необязательный буквенно-цифровой код партии. Первая буква означает тип корпуса ( P —пластмассовый DIP, S- SOIC и т.п. ), вторая —температурный диапазон ( S —стандартный: 0 —700

C, E -расширенный: -40 —1050

C), третья —характеризует защитную оболочку от воздействия окружающей среды ( C — стандартная пластмассовая, E —стандартная герметичная ).

Например, полное обозначение МК Z86E02 может быть следующим:

Z86E0208PSC.

Рис. 1.48. Расположение выводов микроконтроллеров Z8

Для более полной информации следует обратиться к фирменным справочникам [4,5].

ЗАКЛЮЧЕНИЕ

На основе рассмотренных в настоящем пособии материалов можно заключить, что однокристальные микроконтроллеры являются перспективной элементной базой для построения устройств передачи и обработки данных. Они имеют все необходимые атрибуты для решения всех задач, возникающих при проектировании таких устройств. Прежде всего, это аппаратные средства микроконтроллеров, начиная от встроенной памяти программ и данных и кончая размещенными на кристалле периферийными устройствами, а также средствами обеспечения надежной работы в условиях помех. Разнообразие конструктивного исполнения и возможность выбора варианта с низким напряжением питания и жесткими условиями эксплуатации позволяют разработчику всегда подобрать подходящую модель микроконтроллера для своей конкретной задачи. Комплексная система команд, возможность программирования аппаратной конфигурации, режимов резервирования и низкого электромагнитного излучения позволяют при весьма ограниченных объемах встроенной памяти программ решать сложнейшие задачи применения. Фирма Zilog снабжает свои изделия подробной документацией и средствами разработки.

Рассмотренными микроконтроллерами номенклатура продуктов фирмы для устройств передачи и обработки информации не ограничивается. Фирма Zilog производит большое разнообразие микроконтроллеров Z8, микроконтроллеров для цифрового телевидения, для телефонных автоответчиков, цифровых сигнальных процессоров, контроллеров для периферийных устройств и внешней памяти персональных компьютеров, аудио и мультимедиа приборов, специальных микропроцессоров для систем связи [7].

Использование микроконтроллеров для построения устройств передачи и обработки информации позволяет не только улучшить их основные технические характеристики, такие как надежность, быстродействие, точность, массогабаритные характеристики, энергопотребление, но и получить сопровождаемую конструкцию, совершенствование функций которой можно производить без изменения конструкторской документации и перестройки производственного цикла.

|