| Содержание

1.Обзор архитектуры платы L-783. 1

1.1 ВВЕДЕНИЕ В ADSP. 3

1.2 БАЗОВАЯ АРХИТЕКТУРА. 8

1.3. ДРУГИЕ УСТРОЙСТВА НА КРИСТАЛЛЕ. 11

1.4 СИСТЕМА ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ ОТЛАДКИ ПРОЦЕССОРОВ СЕМЕЙСТВА ADSP-2100. 14

2. Подход к решению задачи. 15

2.1 Аппаратная часть. 16

2.2 Подключение сигналов. 21

3 Программное обеспечение: 26

3.1 Создание управляющей программы.. 27

3.2 Загрузка управляющей программы в DSP. 29

4. Реализация. 31

4.1 Сбор данных. 35

5. Вывод. 40

6.Список используемой литературы.. 41

1. Введение

Основная цель работы:

Исследование атмосферы на расстоянии 80-100 км от земли. Исследование проводится путем испускания электромагнитных волн в атмосферу импульсным радаром и прием отраженных волн приемником. Проверяется 8 направлений, 8 радаров.

Необходимая система работает в 3-х режимах:

1. Поиск

2. Селекция

3. Регистрация

Поиск

проводится путём передачи коротких электромагнитных импульсов длиной около 100мкс и приема отраженного сигнала. Принятие нужного происходит не сразу после испускания импульса, а через некоторое время, чтобы не регистрировать ненужные объекты(самолет, стая птиц и т.д.).Импульсы испускаются каждые 2500 мкс.(400Гц) После испускания каждого идет принятие и анализ полученного отражения. Если отражение было, то идет режим селекции

.

Система переходит в режим селекции

после получения отражения сигнала и идет анализ полученных результатов. В этом режиме идет измерение полученных данных – измерение длительности отражения, его амплитуда, соотношение к шуму. Если условия не выполняются, происходит переключения направления. Но если измеренные результаты показывают, что это наш сигнал, происходят ещё такие же 2 проверки. Если следующие 2 проверки показывают такой же результат, то система переключается в режим регистрации

.

В режиме регистрации

система записывает получаемые данные на диск. Радар посылает 80 импульсов и полученное отражение записывается на диск. Даже если отражение пропало или получаемый сигнал не нужный, всё равно продолжается запись на диск в течении этих 80 кадров(80*2500мкс). Далее происходит смена направления и система проходит эти 3 режима заново.

Реклама

Для управления такой системы используется плата L-783, на которой установлен сигнальный процессор ADSP-2185.

2. Обзор ADSP - 2100

Семейство ADSP-2100 представляет собой ряд программируемых процессоров и микрокомпьютеров на одном кристалле, которые объединяет общая базовая архитектура, оптимизированная для цифровой обработки сигналов и других операций в области высокоскоростной обработки цифровых данных. Отличие различных процессоров семейства друг от друга заключается в числе и виде дополнений к базовой архитектуре, а именно: внутренней памяти на кристалле, таймере, последовательных и параллельных портов. Кроме того, процессоры ADSP-21msp58/59 имеют на кристалле аналоговый интерфейс для обработки смешанных аналоговых/цифровых сигналов.

Функциональные устройства:

• Вычислительные устройства - Каждый процессор семейства содержит три независимых вычислительных устройства с полным набором функциональных возможностей: арифметико-логическое устройство (АЛУ), умножитель-накопитель (умножитель) и устройство (циклического) сдвига. Вычислительные устройства обрабатывают данные разрядностью 16 бит и поддерживают вычисления с повышенной точностью.

•Генераторы адреса данных и программный автомат - Два генератора адреса данных и программный автомат генерируют адреса для доступа к памяти на кристалле или внешней памяти. Программный автомат поддерживает команды условного перехода за один цикл и организует выполнение циклов программы с нулевыми затратами ресурсов. Два генератора адреса данных позволяют

одновременно генерировать адреса для выборок двух операндов. Программный автомат и генератор адреса данных обеспечивают постоянную загрузку вычислительных устройств, максимизируя, таким образом, их производительность.

• Память - В семействе ADSP-2100 используется модифицированная гарвардская архитектура, при которой данные хранятся в памяти данных, а память программы содержит как команды, так и данные. Все процессоры семейства ADSP-2100 имеют ОЗУ на кристалле, которое включает часть пространства памяти программы и часть пространства памяти данных. Быстродействие памяти на кристалле позволяет процессору выбирать два операнда (один - из памяти данных, и один - из памяти программы) и команду (из памяти программы) за один цикл.

• Последовательные порты - Последовательные порты обеспечивают полное сопряжение с аппаратными средствами реализации компандирования. Поддерживается компандирование и с А-, и с ^-характеристикой. Порты непосредственно сопрягаются со многими типами последовательных устройств. Каждый порт может генерировать программируемые внутренние тактовые синхроимпульсы или принимать внешние тактовые синхроимпульсы.

Реклама

• Таймер - Программируемый таймер/счетчик с предварительным делителем частоты разрядностью 8 бит обеспечивает генерацию периодических прерываний.

• Порт интерфейса хост-машины - Порт интерфейса хост-машины обеспечивает прямое соединение (без буферных логических схем) с хост-процессором. Порт интерфейса хост-машины имеет 16 выводов для данных и 11 управляющих выводов. Порт интерфейса хост-машины - чрезвычайно гибкое устройство, у которого есть возможности, позволяющие осуществлять простое сопряжение с множеством хост-процессоров. Например, процессоры Motorola 68000, Intel 8051, или другие процессоры семейства ADSP-2100 легко подсоединяются к порту интерфейса хост-машины.

• Порты прямого доступа к памяти - Имеющиеся в процессоре ADSP-2181 порт прямого доступа к внутренней памяти (IDMA) и порт прямого побайтового доступа к памяти (BDMA) обеспечивают эффективную передачу данных в и из внутренней памяти. Внутренний порт доступа к памяти имеет 16-разрядную мультиплексированную шину адреса и данных и поддерживает работу с 24-разрядной памятью программы. Запись данных в этот порт осуществляется асинхронно и не влияет на быстродействие процессора ADSP-2181. Порт прямого доступа к памяти с байтовой организацией позволяет осуществлять начальную загрузку и хранение данных и команд программы.

• Аналоговый интерфейс - Некоторые процессоры семейства имеют на кристалле средства поддержки обработки смешанных аналоговых/цифровых сигналов. Эти средства включают аналогово-цифровой преобразователь (АЦП), цифро-аналоговый преобразователь (ЦАП), аналоговые и цифровые фильтры и средства параллельного сопряжения с базовой архитектурой процессора. Преобразователи используют сигма-дельта модуляцию для получения выборки из сигнала с избыточной дискретизацией.

Архитектура процессоров семейства ADSP-2100 имеет высокую степень параллелизма, отвечающую требованиям цифровой обработки сигналов. За один цикл любой процессор семейства может:

• Сгенерировать новый программный адрес.

• Выбрать следующую команду.

• Выполнить одну или две операции пересылки данных.

• Обновить один или два указателя адреса данных

• Выполнить вычисление.

В течение одного и того же цикла процессоры, имеющие соответствующие функциональные устройства, могут:

• Принять и/или передать данные через последовательный(ые) порт(ы).

• Принять и/или передать данные через порт интерфейса хост-машины.

• Принять и/или передать данные через аналоговый интерфейс.

• Принять и/или передать данные через DMA порты.

Интерфейс системы и памяти

В каждом процессоре семейства ADSP-2100 внутренняя память соединяется с другими функциональными устройствами посредством четырех расположенных на кристалле шин: шины адреса памяти данных, шины данных памяти данных, шины адреса памяти программы и шины данных памяти программы. Одна внешняя шина адреса и одна внешняя шина данных выводятся вне кристала; эти шины могут использоваться для доступа либо к памяти программы, либо к памяти данных.

Внешние устройства могут управлять шинами, формируя сигналы запроса/предоставления шины (BR и BG). Процессоры семейства ADSP-2100 могут продолжать работу, даже если шины предоставлены другому устройству управления, до тех пор, пока не потребуются операции с внешней памятью.

Все процессоры семейства поддерживают отображенные в карте памяти периферийные устройства при помощи генерации программируемых состояний ожидания.

Цепь загрузки обеспечивает автоматическую загрузку памяти программы на кристалле после запуска. Это может быть сделано или через интерфейс памяти с одного СППЗУ, или через порт интерфейса хост-машины с хост-процессора, или через порт прямого побайтового доступа к памяти процессора ADSP-2181. Многочисленные программы могут быть отобраны и загружены без каких-либо дополнительных аппаратных средств.

Процессоры семейства ADSP-2100 отличаются по их ответу на прерывания, инициированные пользователем. Во всех случаях программный автомат позволяет процессору обработать прерывание с минимальной задержкой. Прерывания могут быть расположены в порядке их приоритета без дополнительной задержки. Внешние прерывания могут быть настроены на срабатывание по фронту или по уровню. Внутренние прерывания могут генерироваться таймером, портом интерфейса хост-машины, последовательными портами и портом прямого побайтового доступа к памяти.

Набор команд

Семейство ADSP-2100 имеет унифицированный единый набор команд, постепенно расширяющийся сверху вниз с увеличением степени интеграции. Процессоры ADSP-2171, ADSP-2181 и ADSP-21msp58/59 имеют ряд дополнительных и усовершенствованных команд.

Набор команд семейства ADSP-2100 обеспечивает гибкость в пересылке данных. Многофункциональные команды соединяют одну или более пересылки данных с вычислениями. Каждая команда может быть выполнена за один цикл процессора. В языке ассемблер для читаемости и легкости кодирования используется алгебраический синтаксис. Имеется набор программных и аппаратных средств, обеспечивающих отладку программы.

Рабочие характеристики цифровых сигнальных процессоров

Из-за высоких требований, обусловленных специфическими областями применения сигнальных процессоров, их архитектура и рабочие характеристики отличаются от архитектуры других микропроцессоров и микроконтроллеров. Кроме высокой скорости выполнения команд, цифровой сигнальный процессор должен обладать следующими свойствами:

• Способность быстрого и гибкого выполнения арифметических операций - Базовая архитектура семейства ADSP-2100 обеспечивает вычисление за один цикл операций умножения, умножения с накоплением, произвольной величины сдвига и стандартных арифметико-логических операций. Кроме того, арифметические устройства позволяют осуществлять вычисления в любой последовательности, поэтому не требуется дополнительно модифицировать алгоритм цифровой обработки сигнала.

• Расширенный динамический диапазон - Большие суммарные результаты, типичные в цифровой обработке сигналов, аппаратно поддерживаются в умножителе-накопителе процессоров семейства ADSP-2100. Сумматор разрядностью в 40 бит обеспечивает восемь бит защиты от переполнения при последовательном сложении, и тем самым гарантирует, что не произойдет ни потери данных, ни их диапазона; чтобы произошла потеря старшего разряда, требуется 256 переполнении. Имеются специальные команды для выполнения масштабирования данных с блочной плавающей точкой.

• Возможность выбора двух операндов за один цикл - Для обеспечения вычислений с расширенными суммарными результатами требуется два операнда в каждом цикле. Все члены семейства ADSP-2100 способны поддерживать выполнение двух операндов данных, независимо от того, хранятся ли данные на или вне кристалла.

• Аппаратная поддержка циклических буферов - Для целого класса алгоритмов цифровой обработки сигналов, включая фильтры, требуется реализация циклических буферов. Базовая архитектура процессоров семейства ADSP-2100 включает аппаратное обеспечение циклического возврата указателя адреса, упрощая использование циклических буферов в памяти как на, так и вне кристалла и сокращая потери на их организацию (и, следовательно, увеличивая производительность).

• Организация циклов и условных переходов с нулевыми потерями времени -Алгоритмы цифровой обработки сигналов содержат повторы и в большинстве своем выражаются логически как циклы. Программный автомат в процессорах семейства ADSP-2100 поддерживает код цикла с нулевыми потерями, обеспечивая одновременно отличные рабочие характеристики и ясную структуру программы. Подобным же образом, без потерь ресурсов, организуются условные переходы.

2.1 БАЗОВАЯ АРХИТЕКТУРА

Рис.2 базовая архитектура

Каждый процессор семейства ADSP-2100 содержит три независимых вычислительных устройства с полным набором функциональных возможностей:

арифметико-логическое устройство (АЛУ), умножитель-накопитель (умножитель) и устройство циклического сдвига. Вычислительные устройства обрабатывают данные разрядностью в 16 бит и поддерживают вычисления с повышенной точностью.

В АЛУ выполняются стандартные арифметические и логические операции и примитивы деления. В умножителе за один машинный цикл выполняются операции умножения, умножения/сложения и умножения/вычитания. Устройство сдвига выполняет операции арифметического и логического сдвига, нормализации, денормализации и нахождения порядка числа. Устройство сдвига осуществляет управление числовыми форматами, включая представления чисел, состоящих из нескольких слов, числами с плавающей точкой. Вычислительные устройства соединяются таким образом, что выход любого из этих устройств может быть входом в любое из этих устройств в следующем цикле. Для этого служит внутренняя шина результатов (Р шина) напрямую соединяющая вычислительные устройства.

Все три вычислительных устройства содержат регистры ввода и вывода, доступные по шине данных памяти данных (ДПД). Вычислительные устройства, как правило, берут операнды из регистров ввода и загружают результат в регистры вывода. Эти регистры являются буферами между памятью и вычислительными устройствами. Благодаря этому вводится один уровень конвейерной обработки при вводе и один уровень - при выводе. Р шина позволяет использовать результат одного вычисления напрямую в качестве входного значения для другого вычисления. Это позволяет избежать задержки конвейерной обработки при выполнении серии различных вычислений.

Генераторы адреса и программный автомат

Два специальных генератора адреса данных и программный автомат обеспечивают работу вычислительных регистров с максимальной производительностью. Генераторы адреса данных генерируют адреса памяти, когда данные памяти пересылаются в или из регистров ввода или вывода. Каждый генератор адреса сохраняет до четырех указателей адреса. Когда указатель используется для косвенной адресации, он модифицируется на величину, содержащуюся в заданном регистре. Имея два генератора адреса данных, процессор может одновременно генерировать два адреса для выборок двух операндов.

Каждому указателю может соответствовать значение длины буфера для реализации адресации по модулю при организации циклических буферов. (Свойство циклического буфера также используется в последовательных портах и аналоговом интерфейсе для автоматических передач данных. За дополнительной информацией обратитесь к главе о последовательных портах).

Генератор адреса данных 1 может генерировать адреса только для памяти данных. Генератор адреса данных 2 может генерировать адреса либо для памяти данных, либо для памяти программы. При установке бита соответствующего режима в регистре состояния режима (MSTAT) биты выходного адреса генератора адреса данных 1 переставляются в обратном порядке перед их выводом на шину адреса. Это свойство облегчает организацию бит-реверсной адресации при выполнении быстрого преобразования Фурье (БПФ).

Программный автомат посылает адреса команд в память программы. Программный автомат управляется регистром команд, в котором содержится текущая выполняемая команда. Регистр команд позволяет ввести один уровень конвейерной обработки в поток программы. Команды выбираются и загружаются в регистр команд за один цикл процессора и выполняются в течении следующего цикла, в то время как подготавливается выбор следующей команды. Для сокращения количества холостых циклов программный автомат осуществляет поддержку условных переходов, вызовов подпрограмм и возврата в основную программу за один цикл. Благодаря счетчику циклов и стеку цикла процессор выполняет программу цикла с нулевыми потерями. Никаких дополнительных команд перехода для организации циклов не требуется.

Шины

Внутренние элементы процессора связаны пятью внутренними шинами. Шины адреса памяти программы (АПП) и данных (АПД) используются для адресов, связанных с памятью программы и памятью данных. Шины данных памяти программы (ДПП) и памяти данных (ДПД) используются для передачи данных и кода команд из памят/ данных и памяти программы. Все шины мультиплексированы в одну внешнюю шину адреса и в одну внешнюю шипу данных; сигналы BMS , DMS и PMS выбирают различные адресные пространства. По Р-шине промежуточные результаты напрямую передаются между вычислительными устройствами.

Шина АПП разрядностью 14 бит обеспечивает прямую адресацию до 16К слов смешанного кода программы и данных. Шина ДПП разрядностью 24 бита позволяет передавать 24-битовые команды.

Шина АПД разрядностью 14 бит обеспечивает прямую адресацию до 16К слов данных. Шина ДПД имеет разрядность 16 бит. Шина ДПД обеспечивает передачу содержимого любого регистра в процессор для дальнейшей его передачи в любой другой регистр или любую ячейку памяти за один цикл. Адрес памяти программы может иметь два источника: абсолютное значение, заданное в коде команды (прямая адресация) и значение на выходе генератора адреса данных (косвенная адресация). Только косвенная адресация поддерживается для выборок данных из памяти программы.

Шина ДПП может также использоваться для передачи данных в и из вычислительных устройств напрямую или через устройство обмена данными между шинами ДПП и ДПД. Устройство обмена данными между шинами ДПП и ДПД позволяет согласовывать прохождение данных из одной шины в другую. Оно содержит аппаратные средства для преодоления разницы в 8 бит между разрядностью этих двух шин.

1.3. ДРУГИЕ УСТРОЙСТВА НА КРИСТАЛЛЕ

В этом разделе описываются дополнительные функциональные устройства, которые могут входить в состав процессоров семейства ADSP-2100.

Последовательные порты

Большинство процессоров семейства имеют один или два двунаправленных последовательных порта с двойной буферизацией для последовательной связи. Последовательные порты синхронны и используют синхронизирующие сигналы для управления потоком данных. Каждый последовательный порт может генерировать внутренние тактовые импульсы или использовать внешние. Синхронизирующие сигналы могут генерироваться внутренним или внешним устройством. Длины слов могут варьироваться от 3 до 16 бит. Один последовательный порт (SPORTO) обладает многоканальностью, что позволяет осуществлять прием и передачу дополнительных слов данных из потока данных с 24- или 32-разрядными словами. Второй последовательный порт, SPORT1, может быть по желанию сконфигурирован как два дополнительных вывода внешних прерываний (IRQ1, IRQO) и выход флага "Flag Out" (FO) и вход флага "Flag In" (FI).

Таймер

Таймер с программируемыми интервалами обеспечивает генерацию периодических прерываний. 8-разрядный регистр предварительного деления позволяет осуществлять декрементирование регистра счетчика разрядностью 16 бит через число циклов от 1 до 256. Прерывание генерируется, когда регистр счетчика достигает 0. Регистр счетчика перезагружается из 16-битового регистра периода, и таймер возобновляет свою работу.

Порт интерфейса хост-машины (ADSP-2111, ADSP-2171, ADSP-21msp5x)

Порт интерфейса хост-машины (ХИП) - это параллельный порт ввода/ вывода, который позволяет легко соединять процессор с хост-процессором. Процессоры семейства ADSP-2100 могут подсоединяться через ХИП и отображаться в карте памяти хост-машины как периферийные устройства. ХИП функционирует параллельно и асинхронно с базовой архитектурой процессоров семейства ADSP-2100. Порт интерфейса хост-машины состоит из регистров, через которые процессор семейства ADSP-2100 и хост-машина обмениваются данными и информацией о состоянии. ХИП может быть сконфигуророван для шины данных разрядностью 8 или 16 бит; мультиплексированной шины адреса/данных или отдельных шин адреса и данных; отдельных стробирующих сигналов записи и считывания или стробирующего сигнала записи/считывания и стробирующего сигнала данных.

Порты прямого доступа к памяти (ADSP-2181)

Процессор ADSP-2181 имеет два порта прямого доступа к памяти: порт прямого доступа ко внутренней памяти (IDMA) и порт прямого побайтового доступа к памяти (BDMA). Порт прямого доступа ко внутренней памяти является эффективным средством обмена данными между главной вычислительной системой и цифровым сигнальным процессором. Этот порт используется для доступа ко внутренней памяти программы и памяти данных цифрового сигнального процессора с потерями в один цикл за переданное слово. Порт IDMA имеет мультиплексированную шину адреса и данных разрядностью 16 бит и поддерживает работу с 24-разрядной памятью программы. Запись данных в' порт IDMA осуществляется асинхронно и не влияет на быстродействие процессора. Контроллер прямого доступа к памяти с байтовой организацией позволяет осуществлять загрузку и хранение данных и команд программы, используя пространство памяти с байтовой организацией. Внутренняя схема порта BDMA позволяет обращаться к пространству памяти с байтовой организацией при нормальной работе процессора с издержками в один цикл за переданное слово разрядностью 8, 16 или 24 бита.

Аналоговый интерфейс

Аналоговый интерфейс состоит из входных усилителей и сигма-дельта аналого-цифрового преобразователя (АЦП) разрядностью 16 бит, а также из сигма-дельта цифро-аналогового преобразователя (ЦАП) и выходных усилителей.

1.4 СИСТЕМА ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ ОТЛАДКИ ПРОЦЕССОРОВ СЕМЕЙСТВА ADSP-2100

Семейство ADSP-2100 поддерживается полным набором программных и аппаратных средств отладки. Система отладки процессоров семейства ADSP-2100 включает программные средства отладки, а также эмулятор и EZ-платы™ для устранения аппаратных неисправностей.

Программные средства отладки включают:

• Построитель системы - Построитель системы описывает архитектуру системы при отладке. Он определяет объем доступной внешней памяти ОЗУ/ПЗУ и отображенных в карте памяти портов ввода/вывода для разрабатываемых аппаратных средств, а также расположение памяти программы и данных.

• Ассемблер - Ассемблер компилирует исходный код и модули данных, а также поддерживает синтаксис высокого уровня набора команд. Кроме поддержки

2.1 Аппаратная часть

Платы серии L-7xx

являются современными, быстродействующими и надежными устройствами на базе высокопроизводительной шины PCI 2.1

для ввода, вывода и обработки аналоговой и цифровой информации в персональных IBM-совместимых компьютерах. Благодаря интерфейсу PCI

обеспечивается высокая скорость обмена информацией (данными) с программой пользователя, исключаются конфликты с другими платами, установленными в PC. На платах полностью отсутствуют какие бы то ни было конфигурационные перемычки и переключатели. Все режимы работы таких плат задаются чисто программным образом. Платы L-7xx

можно рассматривать и как удобное средство для многоканального сбора информации, и как законченную систему с собственным процессором, позволяющую искушенному пользователю реализовывать свои собственные алгоритмы обработки данных на уровне программирования установленного на платах сигнального процессора (DSP) фирмы Analog Devices, Inc.

— ADSP-2184/ADSP-2185/ ADSP-2185M/ADSP-2186.

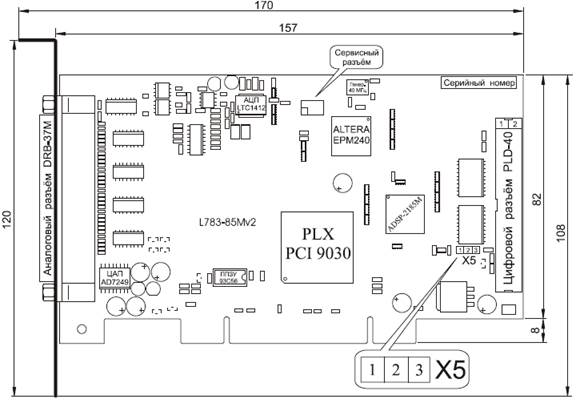

Рис.3 Внешний вид платы L-783M (Rev. C)

Общие технические параметры плат L-7xx

В данном разделе описаны технические параметры АЦП, ЦАП, цифровых линий и внешние условия работы и хранения плат L-7xx

.

Аналого-цифровой преобразователь (АЦП)

На плате установлена одна микросхема АЦП, на вход которой при помощи набора коммутаторов может быть подан усиленный сигнал с одного из 16 или 32 аналоговых каналов на внешнем разъѐме. Типовые характеристики всего входного аналогового тракта приведены в нижеследующей таблице:

Таблица 1. Параметры аналогового тракта.

|

|

|

|

|

|

|

| 16 дифференциальных или 32 с общей землей

|

|

|

|

|

|

| Диапазоны входного сигнала

|

|

| 5В, 1.25В, 0.3125В, 0.078В

|

|

|

| Напряжение синфазного сигнала

|

|

| ±10 В (не зависит от диапазона)

|

|

|

|

L-761

|

L-780

|

L-783

|

| Разрядность, рассчитанная по отношению сигнал/шум на заземленном входе PGA при макс. частоте АЦП

|

|

| Gain=1 13.8 бит

Gain=4 13.6 бит

Gain=16 13.3 бит

Gain=64 12.7 бит

|

|

| Gain=1 11.9 бит Gain=2 11.9 бит Gain=4 11.9 бит Gain=8 11.8 бит

|

|

| Разрядность, рассчитанная по отношению сигнал/(шум+гармоники) полученная при оцифровке синусоидального сигнала частотой 10 кГц с амплитудой 4.9 В при макс. частоте запуска АЦП

|

|

|

|

|

|

|

|

|

| Входное сопротивление при одноканальном

вводе

|

|

|

| Максимальная частота преобразования

|

|

|

|

|

|

|

| При включенном питании компьютера входная защита выдерживает 25В. При выключенном питании входная защита выдерживает 10В.

|

|

| Входной ток не более 20 мА на вход и 80 мА на сумму входов

|

|

| Интегральная нелинейность преобразования

|

|

|

|

| Дифференциальная нелинейность преобразования

|

|

|

|

| Время установления анало-гового тракта при макси-мальном перепаде напряже-ния (точность установления аналогового тракта в %)

|

|

| макс. 5 мкс (точность 0.01%)

|

|

| макс. 1.8 мкс (точность 0.01%)

|

|

| макс. 0.25 мкс (точность 0.1%)

|

|

|

|

L-761

|

L-780

|

L-783

|

| Межканальное прохождение на частоте сигнала 10 кГц, коэффициенте усиления ‗1‘ и макс. частоте запуска АЦП**

|

|

|

|

| Смещение нуля без калибровки

|

|

|

|

Цифро-аналоговый преобразователь (ЦАП)

На плате L-7xx

по желанию пользователя может быть дополнительно установлена микросхема двухканального 12ти битного ЦАП. Т.о. на внешнем аналоговом разъѐме платы появляются две выходных аналоговых линии. Характеристики микросхемы ЦАП приведены в таблице ниже:

Таблица 2. Параметры ЦАП.

|

|

|

|

|

|

| Максимальная суммарная

частота преобразования

|

|

|

|

|

|

|

|

|

|

|

|

Цифровые входы и выходы

На плате имеются цифровые входные и выходные линии ТТЛ-совместимого уровня, которые могут быть использованы пользователем под свои конкретные задачи, например, для управления внешними устройствами и т.д. Параметры цифровых линий приведены ниже в таблице.

Таблица 3. Параметры цифровых линий.

|

|

|

|

|

|

| Напряжение низкого уровня

|

|

|

| Напряжение высокого уровня

|

|

|

| Выходной ток низкого уровня (макс)

|

|

|

| Выходной ток высокого уровня (макс)

|

|

|

|

|

|

1.

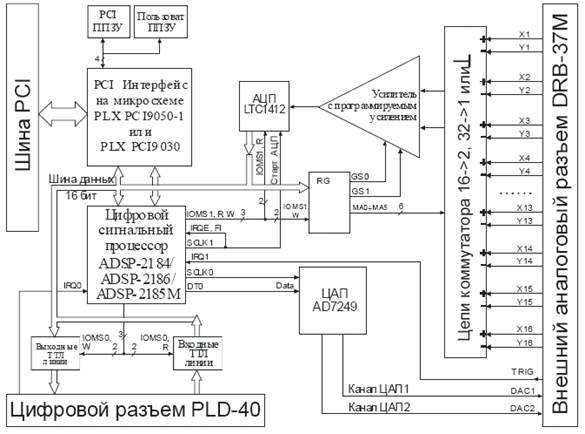

Обзор архитектуры платы L-783

Рис 1. структурная схема платы l-783

На плате расположены микросхема PCI9050-1 или PCI9030 (в зависимости от ревизии платы), полностью обеспечивающая PCI-интерфейс платы с РС, и цифровой сигнальный процессор (DSP), управляющий всей периферией на плате, а именно: АЦП, коммутатором, программируемым усилителем, ЦАП и цифровыми линиями. В зависимости от ревизии на данной плате установлен современный высокопроизводительный сигнальный процессор фирмы Analog Devices, Inc.

ADSP-2184/ADSP-2186 или ADSP-2185M, работающий на частоте 2*fq, где fq=20000.0 кГц – частота кварца. Внутренняя архитектура процессора оптимизирована для реализации таких алгоритмов, как цифровая фильтрация, спектральный анализ и т.д. Сам процессор имеет внутреннюю память программ на 4 КСлов и внутреннюю память данных 4 КСлов (процессор ADSP-2186 обладает 8 КСлов памяти программ и 8 КСлов памяти данных). Наличие такого мощного сигнального процессора обеспечивает возможность самостоятельного применения чрезвычайно гибких методов управления всей периферией платы и позволяет переносить часть операций по обработке данных на саму плату. Процессор обладает своим собственным контроллером ПДП для доступа к любой ячейки внутренней памяти. Благодаря этому Ваша программа может обращаться к любой ячейки памяти процессора, не прерывая работы самого DSP, что исключительно удобно при построении алгоритмов, работающих в реальном масштабе времени. Максимальная пропускная способность обмена данными между сигнальным процессором и компьютером составляет приблизительно 10 Мб/с. Весь обмен данными с центральным компьютером DSP осуществляет через свой канал IDMA. Протокол работы с каналом IDMA предусматривает также возможность загрузки в сигнальный процессор управляющей программы (драйвера), которая будет осуществлять требуемые алгоритмы ввода-вывода. Фирменный драйвер LBIOS

работает по принципу команд и для реализации такой возможности используется прерывание IRQ2

сигнального процессора. Сначала в соответствующую ячейку памяти данных DSP заносится номер команды, которую драйвер должен выполнить. Затем инициируется прерывание IRQ2

, в ответ на которое обработчик данного прерывания, содержащийся в самом LBIOS,

выполняет соответствующие данной команде действия. DSP осуществляет получение данных с АЦП, управляет цепями коммутатора входных сигналов, коэффициентом усиления программируемого усилителя, частотой запуска АЦП и, при необходимости, синхронизацией ввода данных по линии TRIG

внешнего разъёма DRB-37M

. Сигнальный процессор обеспечивает также взаимодействие с микросхемой двухканального ЦАП через посредство своего последовательного порта (SPORT0). Управление внешними цифровыми линиями на разъёме PLD-40

осуществляется DSP с помощью чтения/записи нулевой ячейки своего пространства ввода/вывода (I/O Memory Space).

2.2 Подключение сигналов

Эта глава разъясняет назначение входных и выходных линий на внешних аналоговом и цифровом разъѐмах платы L-7xx

, их характеристики и способы подключения сигналов.

Общие сведения

Подключение сигналов и распайка разъемов возлагаются на пользователя системы. Кабельные части разъѐмов для подключения сигналов содержатся в комплекте штатной поставки. Дополнительно можно приобрести плату клеммников DB-37F-increaser для уменьшения трудозатрат пробного (тестового) монтажа схем при подаче аналоговых сигналов на входы платы.

Межплатные соединения

Когда идѐт одновременная работа сразу с несколькими платами L-7xx

, должны соблюдаться следующие правила:

Если платы между собой соединяются по цифровым линиям (в том числе и по линиям син-хронизации, прерывания), то цепи Digital GND

плат также должны быть соединены между собой.

Если разные платы гальванически связаны между собой по каким-либо цепям, но использу-ют разные компьютеры, то эти PC должны иметь общее заземление (если цепь заземления предусмотрена), а цепи Digital GND

плат должны быть соединены между собой.

Разъ

ѐ

мы плат серии L-7xx

В настоящем разделе приводятся подробные описания разъѐмов L-7xx

с точки зрения внеш-них подключений. Диапазоны напряжений, присутствующие в таблицах при описании сигналов, выведенных на контакты разъемов, всегда приводятся относительно контакта AGND

для аналого-вых сигналов и относительно контакта Digital GND –

для цифровых линий.

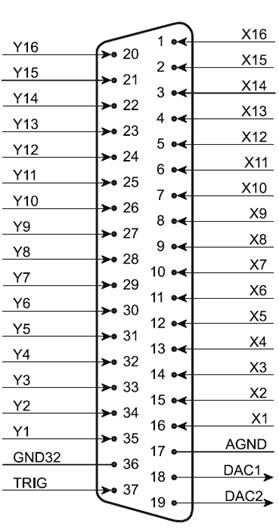

Внешний разъем для подключения аналоговых сигналов

На внешний аналоговый разъѐм DRB-37M

платы выведены линии для работы с аналоговыми сигналами ввода/вывода. Расположение контактов разъѐма и краткое описание их значений приведены ниже в таблице 8

и на рисунке:

Таблица 8. Внешний аналоговый разъ

ѐ

м DRB-37M

|

|

|

|

|

|

|

|

|

| Выход канала 1…2 ЦАП. Диапазон выходного напряжения ±5 В

|

|

|

|

|

|

|

|

|

|

|

| – В однофазном режиме это общий инвертирующий вход каналов 1...32;

– Для всех режимов должен быть подключен к АGND

(в дифференциальном режиме – для увеличения по-мехозащищенности).

|

|

|

|

|

|

| – Неинвертирующий вход каналов 1...16 для диффе-ренциального и однофазного режима;

– Рабочий диапазон напряжения ±10 В;

– Неиспользуемые входы X<1...16>

рекомендуется подключать к AGND

.

|

|

|

|

|

|

| – Инвертирующий вход каналов 1...16 для дифференциального режима;

– Вход каналов 17...32 для однофазного режима;

– Рабочий диапазон напряжения ±10 В;

– Неиспользуемые входы Y<1...16>

рекомендуется подключать к AGND

.

|

|

|

|

|

|

| – Вход внешней цифровой синхронизации сигнала;

– Совместим с выходным логическим уровнем TTL/СMOS элементов с напряжением питания +5 В.

|

|

Рис.4 Внешний разъем DRB-37M

Внутренний разъ

ѐ

м для подключения цифровых сигналов

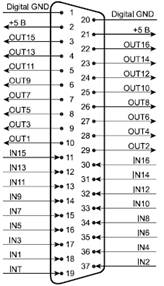

На внутренний разъѐм PLD-40

платы L-7xx

выведены линии для работы с цифровыми сигналами ввода/вывода. Расположение контактов разъѐма и краткое описание их значений приведены ниже в таблице 9

и на рисунке:

Таблица 9. Внутренний цифровой разъ

ѐ

м PLD-40

|

|

|

|

|

|

|

|

|

| 16ти битный цифровой вход: IN1

– младший бит (0ой бит), IN16

– старший бит (15ый бит).

|

|

|

|

|

|

| 16ти битный цифровой выход: OUT1

– младший бит (0ой бит), OUT16

– старший бит (15ый бит).

|

|

|

|

|

|

|

|

|

|

|

| Выход нестабилизированного напряжения +5 В для питания внешних цепей (берѐтся прямо с PCI

шины). Рекомендованная величина максимального тока не более 200 мА.

|

|

|

|

|

|

| – Вход внешней цифровой синхронизации сигнала;

– Совместим с выходным логическим уровнем TTL/СMOS элементов с напряжением питания +5 В.

|

|

Рис. 5 Внутренний разъем PLD-40

Дополнительный кабель AC-7xx-f

Кабель AC-7xx-f

можно использовать в качестве транслятора цифровых линий с внутреннего разъѐма PLD-40

на заднюю панель компьютера. Выходной разъем кабеля – розетка DB-37

. Это означает, что невозможно перепутать этот разъѐм с внешним аналоговым разъѐмом платы. Краткое описание контактов разъѐма смотри в таблице 9. Расположение контактов разъѐма приведено на рисунке ниже:

Рис.6 Дополнительный кабель AC-7xx-f

3.1 Разработка управляющей программы

У пользователя, как правило, не появляется необходимость в написании своих собственных управляющих программ для данной платы, т.к. все наиболее часто требуемые алгоритмы работы уже реализованы в фирменном драйвере, находящимся в файле L783.bio. Однако если же все-таки возникла необходимость в создании собственной управляющей программы (например, для формирования какого-либо специализированного алгоритма действия процессора), то для этого придется освоить достаточно несложный язык ассемблера для сигнального процессора. В качестве законченного примера программирования платы на таком языке можно использовать исходные тексты фирменного драйвера, хранящиеся в файлах DSP\L783\L783.DSP и DSP\L783\*.H.

Процесс формирования собственной управляющей программы:

1. изучить архитектуру процессора ADSP-218x, а также освоить язык его программирования (ассемблер для DSP). Всю подроб-ную информацию об этом можно найти в оригинальной книге “ADSP-2100 Family User’s Manual (Includes ADSP-2171, ADSP-2181)”, Analog Devices, Inc., Third Edition, September 1995

или в русском переводе “Руководство пользователя по сигнальным микропроцессорам семейства ADSP-2100”, под редакцией А.Д.Викторова, Санкт-Петербург, 1997

. Оба эти издания можно приобрести в ЗАО «Л-Кард». Описание и примеры программ для DSP с исходными текстами приводятся в двухтомном справочнике “Digital Signal Processing Applications Using the ADSP-2100 Family”, Analog Devices, Inc.

, который можно найти у официальных российских дистрибьюторов компании Analog Devices, Inc.

(например, фирмы Autex Ltd.

или Argussoft Co.

). Много полезного в дополнение к указанной документации можно обнаружить также на сайте www.analog.com.

2. Процессоры семейства ADSP-21хх поддерживаются полным набором программных средств отладки. Этот пакет включает в себя несколько программ: построитель системы (bld21.exe), ассемблер (asm21.exe), линкер или редактор связей (ld21.exe) и т.д. Все эти программы очень подробно описываются в оригинальной книге “ADSP-2100 Family Assembler Tools & Simulator Manual”, Analog Devices, Inc., Second Edition, November 1994

, которую можно найти у официальных российских дистрибьюторов компании.

Analog Devices, Inc.

(например, фирмы Autex Ltd.

или Argussoft Co.

). Сам пакет разработчика программ для сигнальных процессоров семейства ADSP-21xx, содержащий все вышеуказанные средства отладки (кроме bld21.exe), можно приобрести в ЗАО «Л-Кард». В качестве архитектурного файла нужно использовать L783.ACH.

3. Надо создать соответствующие файлы с исходным кодами Вашей программы на языке ассемблер DSP. Затем эти файлы необходимо оттранслировать (asm21.exe) и скомпоновать с помощью редактора связей (ld21.exe), формируя, таким образом, выполняемую программу типа .EXE, так называемый файл отображения в памяти (memory image file). Формат сформированного файла отображения в памяти очень подробно описан в “ADSP-2100 Family As-sembler Tools & Simulator Manual”, Appendix B

“File Format”, B.2

“Memory Image File (.EXE)”, Analog Devices, Inc., Second Edition, November 1994

. Именно в этом файле содержатся все коды инструкций Вашей программы с соответствующими адресами их расположения в памяти программ DSP, а также инициализирующие значения Ваших переменных и адреса их нахождения в памяти данных. Зная всю эту информацию нужно загрузить ее в память DSP по надлежащим адресам. Для упрощения процедуры загрузки полученный файл отображения в память .EXE преобразуется с помощью утилиты DSP\L783\BIN3PCI.EXE в файл .BIO

4. Реализация

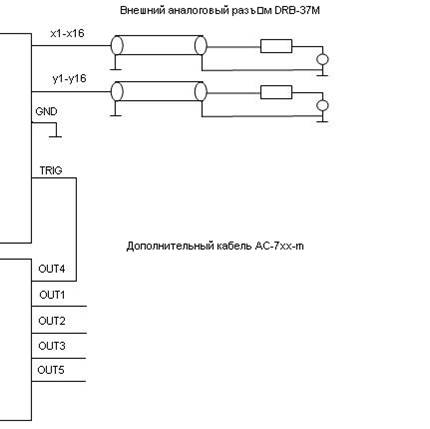

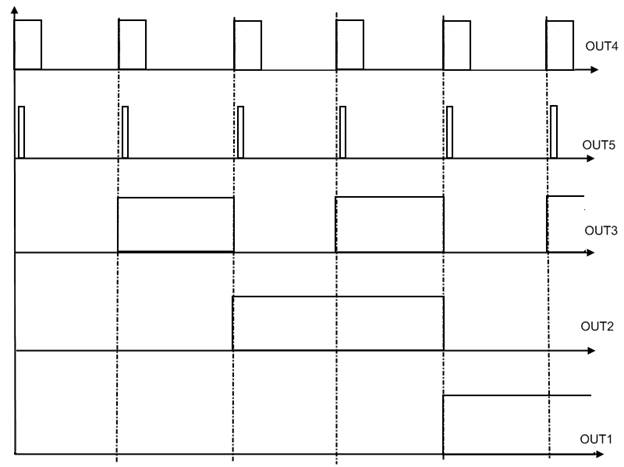

Линия TRIG

на внешнем разъёме DRB-37M

, которая подключена к ножке прерывания IRQE

сигнального процессора (по фронту). Данное прерывание IRQE

генерируется при отрицательном перепаде импульса (|_|) длительностью не менее 50 нс. В фирменном драйвере эта линия используется для цифровой синхронизации ввода данных с АЦП. Эта линия нужна для синхронизации приема данных с АЦП и бланком. При наличии сигнала в OUT4, в это время данные с АЦП не считываются. OUT1-OUT3 Это цифровые выходы, управляющие антенным коммутатором. OUT5 – Импульс испускаемый радиолокатором.

Рис. 10 Подключение

Поиск

проводится путём передачи коротких электромагнитных импульсов длиной около 100мкс и приема отраженного сигнала. Принятие нужного происходит не сразу после испускания импульса, а через некоторое время, чтобы не регистрировать ненужные объекты(самолет, стая птиц и т.д.).Импульсы испускаются каждые 2500 мкс.(400Гц) После испускания каждого идет принятие и анализ полученного отражения.

Для реализации этого режима используются цифровые TTL выходы, АЦП и цифровой сигнальный процессор ADSP 2185, установленный на плате L-783. В данном режиме, задействованы 5 цифровых выходов, и вход АЦП.

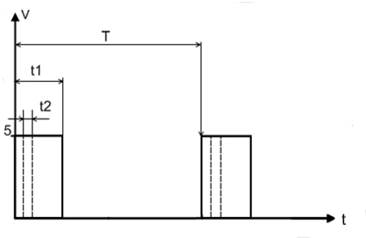

С периодом равным T, вывод OUT4 генерирует бланк, длительностью t1, и вывод импульсa с OUT5 длительностью t2. Бланк необходим для «отбрасывания» не нужных, ранних отражений от близких объектов, чье расстояние над землей меньше, чем 80-100 км (Птицы, самолет, …). Импульс с out5, необходим, для испускания радаром электромагнитного импульса. Работой всей платы занимается Сигнальный процессор, который работает под уже поставляемый драйвер. Для наших целей необходимо модифицировать уже поставляемый драйвер.

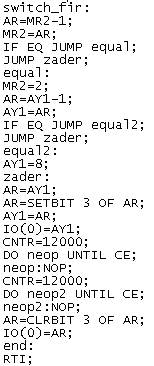

Рис. 11 Вывод бланков по таймеру.

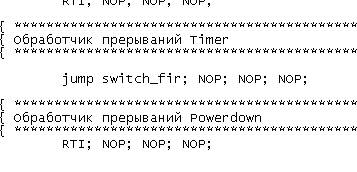

Для создания бланков с периодом T мы решили использовать таймер ADSP. Для этого мы должны настроить таймер на 2500 мкс, чтобы он через данное время генерировал прерывания, и написать обработчик прерывания от таймера.

Рис. 12 инициализация обработчика прерывания в таблице прерыаний

Обработчик прерывания представляет собой подпрограмму, которая управляет состоянием TTL линии.

Рис.13 Описание обработчика прерываний по таймеру

Каждые 2500 мкс Генерируются бланки и импульсы с цифровых линий OUT4 и OUT5. Каждое прерывание линии OUT1,OUT2,OUT3 выводят определенный сигнал, (инкрементируется состояние TTL линий).

Рис. 14 Временная диаграмма ТТЛ линий

Как только состояние OUT1,OUT2,OUT3 будет равным «1»(иначе говоря, 8-е направление), то следующее прерывание выставляет эти линии в «0» и инкрементирование начинается заново.

3.2

Разработка приложения для Windows

Перед началом работы с платой необходимо ее “оживить”, т.е. загрузить в DSP либо фирменный драйвер, находящийся в файле L783.bio, либо Вашу собственную управляющую программу. Только

после выполнения такой процедуры плата будет корректно работать с функциями штатной или Вашей (если создадите) библиотеки.

Коды инструкций сигнального процессора из этого файла необходимо расположить по соответствующим адресам памяти программ, также как данные, инициализирующие переменные драйвера, в памяти данных и запустить управляющую программу на выполнение. Все это и называется загрузка управляющей программы в DSP.

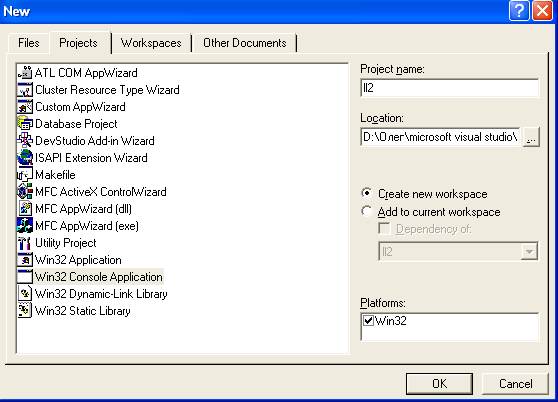

Для создания программы, которая загружает управляющую программу в DSP и управляет платой L-CARD из среды WINDOWS, мы использовали среду разработки MS VISUAL C++ 6.0

Для этого создаем новый проект:

File-new-project-WIN32 console application

Рис.7 Создание проекта

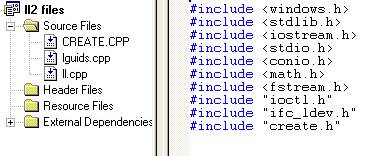

После того, как создали проект, необходимо прикрепить к нему необходимые библиотеки, с помощью которых мы сможем управлять платой L-783. Требуемые библиотеки имеют названия «lguids.cpp»,«create.cpp», «lguids.h» и «create.h» (первые две необходимо добавить в проект , project-add to project – files)

Рис. 8 подключение библиотек

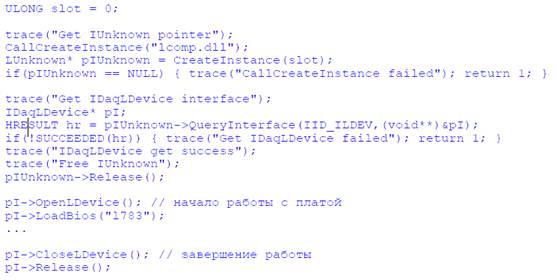

Общий принцип работы с библиотекой:

• Загрузить библиотеку с помощью LoadLibrary.

• Создать объект, связанный с конкретным виртуальным слотом при помощи вызова CreateInstance.

• Получить указатель на интерфейс вызвав QueryInterface

• Далее вызывать функции этого интерфейса.

Виртуальные слоты это собственно порядковые числа в названиях линков драйверов. Начинаются с 0 и так далее по порядку. Разделения на ISA,PCI или USB платы нет. Причем определить, что за плата соответствует конкретному слоту, можно, только открыв его и прочитав информацию GetSlotParam и ReadPlataDescr (+ для L1450, E440, E2010 предварительно надо загрузить плату). GetSlotParam даст информацию о типе платы и назначенных ей ресурсах. Далее для PCI плат более подробную информацию даст ReadPlataDescr. Для L-1450, E440, E2010 также можно вызвать ReadPlataDescr, но предварительно в нее надо загрузить БИОС. Вызов ReadPlataDescr обязателен перед началом конфигурирования сбора данных, поскольку там содержится информация о частоте кварца необходимая при расчетах временных параметров сбора данных. Также там хранятся калибровочные коэффициенты.

В основном файле вашей программы, для работы с платой необходимо написать:

Рис. 9 Подготовка платы к работе

Всё готово, в плату загружен ваш БИОС и теперь можно приступать к работе с платой используя функции библиотек.

В режиме регистрации

система записывает получаемые данные на диск. Радар посылает 80 импульсов и полученное отражение записывается на диск. Даже если отражение пропало или получаемый сигнал не нужный, всё равно продолжается запись на диск в течении этих 80 кадров(80*2500мкс).

Для регистрации данных используется установленный на плате АЦП.

АЦП может записывать данные с частотой до 3 Мгц. В нашей системе достаточно записывать частотой 1 Мгц. Для записи на жесткий диск компьютера мы решили написать программу для ОС Windows, которая при запуске устанавливает параметры платы и начинает считывание записанных данных с АЦП в память компьютера. Происходит это следующим образом: Данные с АЦП заносятся в FIFO-буфер платы, после заполнения половины буфера, плата генерирует прерывания в PC и данные, по шине DMA, заносятся в кольцевой буфер компьютера. После этого можно считывать данные с буфера компьютера.

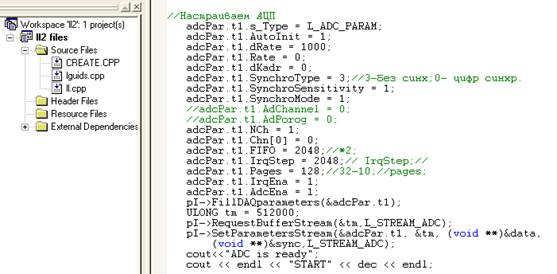

Для начала после того, как мы подготовили нашу программу для работы с платой L-783, мы должны настроить и инициализировать АЦП.

Рис.15 Проект в MSvisual c++

На рисунке описаны настройки параметров АЦП:

ULONG AutoInit

- флаг указывающий на тип сбора данных 0 - однократный 1 -

циклический;

double dRate

- частота опроса каналов в кадре (кГц);

double dKadr

- интервал между кадрами (мс);

double dScale

- масштаб работы таймера для 1250 или делителя для 1221;

ULONG Rate

- частота опроса каналов в кадре (в кодах для процессора,

вычисляется библиотекой);

ULONG Kadr

- интервал между кадрами (в кодах для процессора, вычисляется

библиотекой);

ULONG Scale

- масштаб работы таймера для 1250 или делителя для 1221 (в кодах

для процессора, вычисляется библиотекой);

ULONG FPDelay

- служебная величина задержки выдачи первого отсчета

(вычисляется библиотекой);

ULONG SynchroType

- тип синхронизации;

ULONG SynchroSensitivity

- вид синхронизации;

ULONG SynchroMode

- режим синхронизации;

ULONG AdChannel

- канал, по которому выполняется синхронизация;

ULONG AdPorog

- уровень синхронизации;

ULONG NCh

- количество опрашиваемых каналов ;

ULONG Chn[128]

- массив с номерами каналов и усилением на них; описывает

порядок опроса каналов;

ULONG FIFO

- размер половины аппаратного буфера FIFO на плате;

ULONG IrqStep

- шаг генерации прерываний

После инициализации и настройки АЦП можно начинать считывать данные. Для этого у нас известны все параметры: Размер FIFO-буфера, размер кольцевого буфера, и адрес начала кольцевого буфера - data.

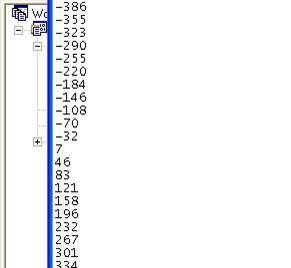

Результаты

Полученные результаты являются результатами не реальной системы, а смоделированной. Получаемый сигнал генерируется искусственно, генератором. Все данные заносятся в файл 1.txt, его можно просмотреть любым текстовым редактором и увидеть:

Рис. 17 Полученные данные с платы l-783

Данные заносятся с частотой dRate

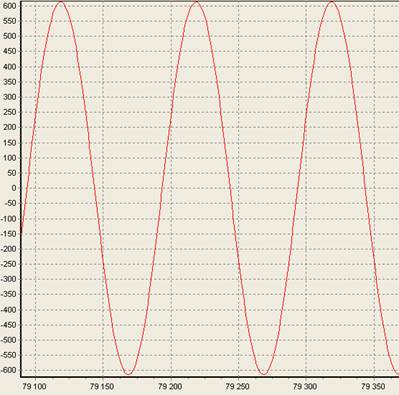

, и построив график по этим точкам можно увидеть сигнал генератора:

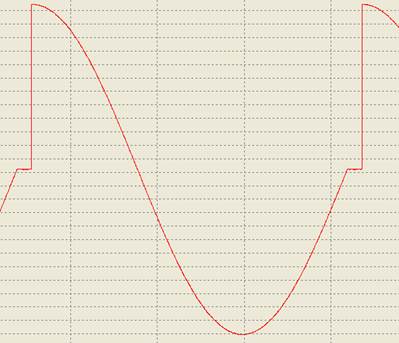

Рис.18 считывание синусоиды с частотой 10 Кгц фирменным драйвером.

Так можно использовать программу, для обычного считывания данных. Но для одновременного формирования Бланков, смены направления(изменения состояния TTL линий) необходимо, использовать наш модифицированный драйвер.

Для этого необходимо поменять файл l783.bio в папке с нашей программой, на наш измененный l783.bio.

Рис. 19 Считывание синусоиды с частотой 500 гц под управлением модифицированного драйвера.

Из рисунка мы видим, что процессор на время выполнения бланка не принимает данные с АЦП и не заносит их в буфер. На 600 мкс, на время бланка сигнал, как и требовалось, не принимается.

5. Заключение

Мы изучили архитектуру платы фирмы L-CARD L-783. Изучили Архитектуру процессора ADSP 2185. На основе полученных знаний сформировали «бланки» и смену направлений через ТТЛ выходы. Сформировали сбор данных с АЦП с частотой 1 Мгц.

В дальнейшем предстоит сформировать обработку полученных данных из АЦП с помощью сигнального процессора ADSP-2185 и логику поиска и регистрации цели.

6.Список используемой литературы

1.Руководство пользователя PCI плат L-761, L-780 и L-783 http://www.lcard.ru/download/l7xx_users_guide.pdf

2. Руководство программиста под DOS для PCI плат L-761, L-780 и L-783 http://www.lcard.ru/download/l7xx_programmers_guide.pdf

3. Информационные заметки для PCI плат L-761, L-780 и L-783 http://www.lcard.ru/download/l7xx_info_notes.zip

4. А. В. Гарманов. Подключение измерительных приборов, решение вопросов электросовместимости и помехозащиты. L-Card, 2003. http://www.lcard.ru/download/lcardconnects.pdf

5. Крис Паппас, Уильям Мюррей - Visual C++ 6. Руководство разработчика

6. А.В. Комаров, Цифровые сигнальные процессоры

7. Цифровые процессоры обработки сигналов семейства ADSP-218x: Учеб.

Пособие /А.А.Зайцев, Т.В.Евдокимова; Рязан. гос. радиотехн. акад. Рязань, 2005. 44с.

8. Руководство пользователя по сигнальным микропроцессорам семейства

ADSP-2100/ Под ред. А.Д. Викторова. СПб гос. электротехнический университет. –СПб, 1997. – 520с.:ил.

|