Пензенская государственная технологическая академия

Кафедра электроники и электротехники

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовому проекту по дисциплине:

"Электроника и микросхемотехника"

на тему:

«Разработка генератора кодовых последовательностей импульсов на интегральных схемах»

Пенза 2007 г.

Содержание

Введение

1. Разработка структурной схемы

2. Синтез функциональных блоков

2.1 Разработка генератора кодов

2.1.1 Выбор варианта структуры генератора кодов

2.1.2 Синтез комбинационной схемы на логических элементах

2.1.3 Синтез комбинационной схемы на мультиплексорах

2.2 Разработка блоков контроля кодовых комбинаций

2.2.1 Синтез блока контроля ошибочных комбинаций на логических элементах

2.2.2 Синтез блока контроля ошибочных комбинаций на мультиплексорах

2.2.3 Синтез блока контроля заданных комбинаций на логических элементах

2.2.4 Синтез блока контроля заданных комбинаций на мультиплексорах

2.3 Сравнительный анализ и выбор оптимального варианта функциональной схемы

3. Разработка принципиальной схемы

3.1 Выбор элементной базы

3.2 Выбор схемы и расчет генератора тактовых импульсов

3.3 Расчет схемы начальной установки

3.4 Расчет конденсаторов развязки по цепи питания

3.5 Расчет длительности переходного процесса

3.6 Расчет потребляемой мощности

3.7 Оценка показателей надежности

4. Моделирование отдельных узлов генератора в программе «ElectronicsWorkbench»

Заключение

Литература

Введение

Цель выполнения курсового проекта состоит в закреплении теоретических знаний по схемным принципам построения устройств вычислительной техники, а также в приобретении практических навыков проектирования конкретных цифровых устройств. Для успешного осуществления работы необходимо уметь: подбирать и использовать литературные источники и нормативные документы; выявлять аналоги и обоснованно выбирать оптимальные технические решения; грамотно применять методы синтеза и анализа микроэлектронных узлов; оформлять схемную и текстовую документацию согласно требованиям ЕСКД.

Элементной базой современных вычислительных устройств служат большие и сверхбольшие интегральные схемы (ИС), в том числе программируемые логические ИС (ПЛИС), которые проектируются автоматизированными методами с помощью ЭВМ. Однако, внутренние структуры таких ИС представляют сочетания все тех же типовых узлов (логических элементов, комбинационных и последовательностных блоков), которые продолжают выпускаться в виде автономных ИС средней степени интеграции. Реализация проектируемого устройства на ИС средней интеграции предполагает определенную свободу выбора элементов с учетом их назначения и особенностей применения, а также позволяет проявить элементы творчества в процессе их сопряжения.

Реклама

Можно выделить следующие основные этапы проектирования:

* этап формирования технического предложения и структурного проектирования на основе анализа задания и уровня техники в данной области;

* этап функционального проектирования с выявлением общих технических решений и принципов функционирования;

* этап схемотехнического проектирования на основе выбранной элементной базы с поиском принципиальных решений узлов, расчетом режимов элементов и оценкой технических показателей функционирования. Итогом данного этапа является разработанная схемная конструкторская документация;

* этап экспериментального исследования спроектированного устройства с целью подтверждения его работоспособности.

Техническим заданием на работу предусмотрено проектирование генератора последовательности двоичных слов. Подобный генератор может использоваться для формирования микропрограмм управления технологическим процессом, для генерирования измерительной последовательности импульсов, для образования цифровых сообщений при передаче информации по линии связи. объем проекта в его содержании по существу относительно невелик, устройство в зависимости от предпочтений исполнителя может содержать от 10 до 20 корпусов ИС средней интеграции. В то же время работа охватывает основные этапы проектирования от поиска возможных вариантов структуры до получения электрической принципиальной схемы с проверкой ее работоспособности.

Материалы проекта изложены в пояснительной записке и приложениях к ней, включающих принципиальную электрическую схему разработанного устройства и перечень входящих в нее элементов. Результатом работы является создание устройства, доведенного до уровня практической реализации и проверенного экспериментально путем компьютерного моделирования.

1. Разработка структурной схемы

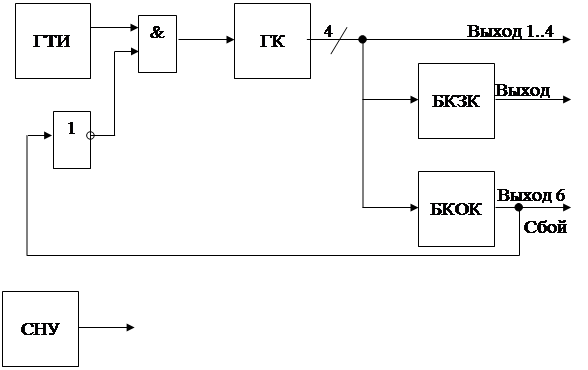

В структуру разрабатываемого устройства необходимо включить генератор тактовых импульсов, снабжающий остальные блоки синхросигналами. Наряду с генератором тактовых импульсов основным блоком служит собственно генератор кодов, представляющий собой цифровой автомат. Для обеспечения функционирования устройства и проверке комбинаций на правильность необходимо предусмотреть блок контроля ошибочных комбинаций и блок контроля заданной комбинации. Структурная схема устройства представлена на рисунке 1.1.

Реклама

В схеме приняты обозначения:

ГТИ – генератор тактовых импульсов;

ГК – генератор кодов;

БКЗК – блок контроля заданной комбинации;

БКОК – блок контроля ошибочных комбинаций;

СНУ – схема начальной установки

Рис. 1.1. Структурная схема устройства

Работа схемы начинается после подачи питающего напряжения. Схема начальной установки приводит в исходное состояние все функциональные блоки. После этого начинает работать генератор тактовых импульсов, который подает импульсы на генератор кодов, который в свою очередь вырабатывает на своих выходах заданные кодовые комбинации. Кроме того, во время работы блок контроля ошибочных комбинаций вырабатывает один сигнал, который поступает на логический ключ, где разрешается или запрещается выработка кодовых комбинаций, если в ходе проверки будет обнаружена незапланированная комбинация, то блок контроля ошибочных комбинаций вырабатывает управляющий сигнал для блокировки сигналов с генератора тактовых импульсов. Также в схеме предусмотрен блок контроля заданной комбинации, который проверяет кодовую комбинацию, заданную изначально при разработке, для проверки правильности работы устройства. При подробном рассмотрении генератор кодов выполнен на основе двоично-десятичного счетчика и преобразователя кодов.

2. Синтез функциональных блоков

При проектировании любого технического устройства возникает вопрос об оптимизации его структуры по какому-либо критерию, дающему основания для сравнения и выбора наилучшего варианта. Согласно заданию при разработке следует стремиться к минимуму затрат аппаратуры. В тоже время следует учитывать и другие важные аспекты дальнейшего использования устройства, в частности при прочих равных условиях преимущество следует отдать вариантам с минимальным потреблением мощности источников питания и вариантам, обеспечивающим наиболее высокую помехоустойчивость и надежность. Дополнительный критерий, которым необходимо руководствоваться при выборе применяемых элементов схем, это их стоимость.

2.1 Разработка генератора кодов

2.1.1 Выбор варианта структуры генератора кодов

Существует несколько вариантов разработки структуры генератора кодов:

1. генератор кодов строится на основе отдельных триггеров и комбинационной схемы, которая обеспечивает на выходах триггеров заданные комбинации двоичных чисел;

2. на основе регистра сдвига и комбинационной схемы, такой вариант построения генератора кодов возможен, если каждое последующее двоичное число получается путем сдвига предыдущего двоичного числа на один разряд вправо или влево;

3. построение генератора кодов на основе двоичного счетчика с модулем счета 10 и комбинационной схемы (преобразователя кодов).

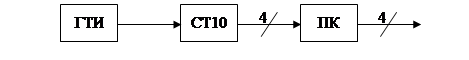

Проанализировав задание и возможные варианты структуры генератора кодов, наиболее подходящим для разработки данного генератора является третий вариант, представленный на рис. 2.1.

Рис. 2.1. Структура генератора кодов

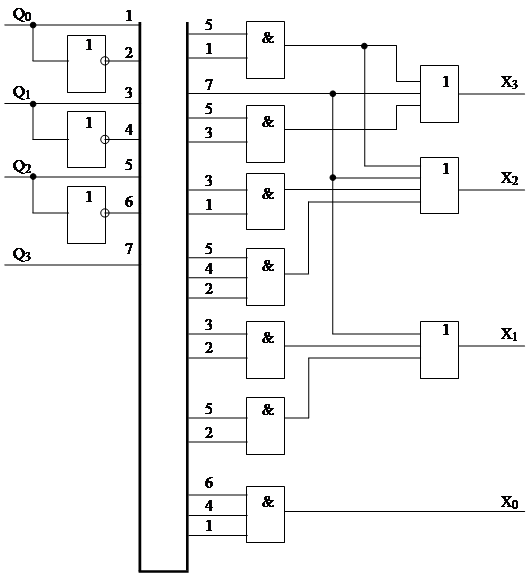

2.1.2 Синтез комбинационной схемы на логических элементах

Необходимо сформировать следующую циклическую последовательность десяти 4-разрядных слов:

0000, 0101, 0010, 0100, 0110, 1000, 1010, 1100, 1110, 1111.

Поскольку счетчик имеет модуль счета равный 10. Составим таблицу истинности для выходных функций Х3

, Х2

, Х1

, Х0

четырех аргументов Q3

, Q2

, Q1

, Q0

(табл. 1.1). Так как число аргументов менее шести, то наиболее просто минимизация осуществляется с помощью карт Карно, в которые построчно переносятся значения функций для каждой комбинации аргументов.

Таблица 2.1

| Выходы счетчика СТ10 |

Выходы генератора |

| Q3

|

Q2

|

Q1

|

Q0

|

X3

|

X2

|

X1

|

X0

|

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

| 0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

| 0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

| 0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

| 0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

| 1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

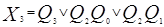

Составим карту Карно и уравнение для Х3

:

| Q1

Q0

|

| Q3

Q2

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

| 01 |

0 |

1 |

1 |

1 |

| 11 |

x |

x |

x |

x |

| 10 |

1 |

1 |

x |

x |

Составим карту Карно и уравнение для Х2

:

|

Q1

Q0

|

| Q3

Q2

|

00 |

01 |

11 |

10 |

| 00 |

0 |

1 |

1 |

0 |

| 01 |

1 |

0 |

1 |

0 |

| 11 |

x |

x |

x |

x |

| 10 |

1 |

1 |

x |

x |

Составим карту Карно и уравнение для Х1

:

|

Q1

Q0

|

| Q3

Q2

|

00 |

01 |

11 |

10 |

| 00 |

0 |

0 |

0 |

1 |

| 01 |

1 |

0 |

0 |

1 |

| 11 |

x |

x |

x |

x |

| 10 |

1 |

1 |

x |

x |

Составим карту Карно и уравнение для Х0

:

|

Q1

Q0

|

| Q3

Q2

|

00 |

01 |

11 |

10 |

| 00 |

0 |

1 |

0 |

0 |

| 01 |

0 |

0 |

0 |

0 |

| 11 |

x |

x |

x |

x |

| 10 |

0 |

1 |

x |

x |

Рис. 2.2. Комбинационная схема на логических элементах

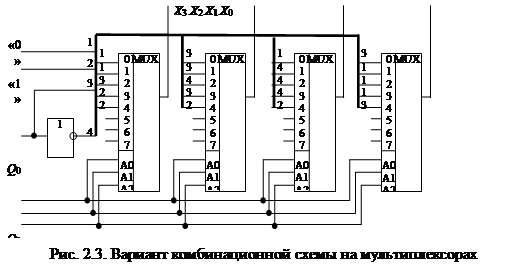

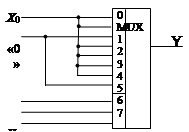

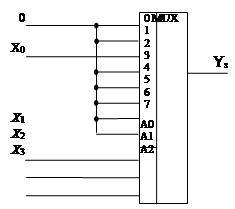

2.1.3 Синтез комбинационной схемы на мультиплексорах

Модификации этой схемы основаны на применении типовых комбинационных узлов средней интеграции: мультиплексоров, дешифраторов, ПЗУ, ПЛМ и др. Рассмотрение возможных модификаций необходимо для того, чтобы составить базу сравнения и оптимизации структуры устройства. С этой целью рассмотрим вариант реализации комбинационной схемы на мультиплексорах.

Количество мультиплексоров в комбинационной схеме должно быть равным количеству выходных функций - числу разрядов выходных слов, которое в нашем примере равно четырем. Каждый мультиплексор должен иметь по 3 адресных входа (по числу аргументов) и, соответственно, по 8 информационных входов, которые подключаются к шинам логических 0 или 1 согласно таблице истинности, аргументы Q3

, Q2

, Q1

определяют адрес одновременно всех мультиплексоров, они не меняются для пары смежных строк таблицы истинности. В каждой паре строк определяется отношение каждой выходной функции Х3

… Х0

к оставшемуся аргументу Q0

(см. табл.2.2).

Таблица 2.2

По табл. 2.2 выполняется подключение информационных входов мультиплексоров с порядковыми номерами, соответствующими данному адресу, к одной из четырех шин:  . .

2.2 Разработка блоков контроля кодовых комбинаций

Блок контроля кодовых комбинаций предназначен для обнаружения незапланированных комбинаций, которые могут возникнуть при включении питания или в результате сбоя. Блок контроля кодовых комбинаций может быть реализован, как и любая комбинационная схема, разнообразными способами (на логических элементах, на мультиплексорах и т.д.).

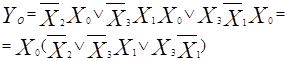

2.2.1 Синтез блока контроля ошибочных комбинаций на логических элементах

Для синтеза блока контроля ошибочных комбинаций на логических элементах составим таблицу истинности (табл. 2.3), в которой выходная функция Yо

приравнивается к значению «лог. 0» на предусмотренных заданием наборах выходных переменных генератора кодов X3

..X0

, и значение «лог. 1» на незапланированных наборах. Далее заполним карту Карно для функции Yо

, и запишем саму функцию, затем реализуем ее на схеме.

Таблица 2.3

| X3

|

X2

|

X1

|

X0

|

Yо

|

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

1 |

1 |

| 0 |

0 |

1 |

0 |

0 |

| 0 |

0 |

1 |

1 |

1 |

| 0 |

1 |

0 |

0 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

0 |

| 0 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

1 |

| 1 |

0 |

1 |

0 |

0 |

| 1 |

0 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

0 |

| 1 |

1 |

0 |

1 |

1 |

| 1 |

1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

0 |

Составим карту Карно и уравнение для Yо

:

|

X1

X0

|

| X3

X2

|

00 |

01 |

11 |

10 |

| 00 |

0 |

1 |

1 |

0 |

| 01 |

0 |

0 |

1 |

0 |

| 11 |

0 |

1 |

0 |

0 |

| 10 |

0 |

1 |

1 |

0 |

Рис. 2.4. Комбинационная схема блока контроля ошибочных комбинаций на логических элементах

2.2.2 Синтез блока контроля ошибочных комбинаций на мультиплексорах

Для построения блока контроля ошибочных комбинаций на мультиплексоре необходимо в таблицу 3 добавить два дополнительных столбца: номер информационного входа мультиплексора и информация на этом входе. Измененная таблица представлена в таб. 2.4.

Таблица 2.4

| X3

|

X2

|

X1

|

X0

|

Yо

|

№ входа |

информация |

| 0 |

0 |

0 |

0 |

0 |

D0 |

X0

|

| 0 |

0 |

0 |

1 |

1 |

| 0 |

0 |

1 |

0 |

0 |

D1 |

X0

|

| 0 |

0 |

1 |

1 |

1 |

| 0 |

1 |

0 |

0 |

0 |

D2 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

0 |

D3 |

X0

|

| 0 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

0 |

D4 |

X0

|

| 1 |

0 |

0 |

1 |

1 |

| 1 |

0 |

1 |

0 |

0 |

D5 |

X0

|

| 1 |

0 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

0 |

D6 |

X0

|

| 1 |

1 |

0 |

1 |

1 |

| 1 |

1 |

1 |

0 |

0 |

D7 |

0 |

| 1 |

1 |

1 |

1 |

0 |

Рис. 2.5. Блок контроля ошибочных комбинаций на мультиплексорах

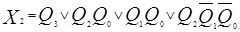

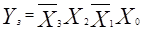

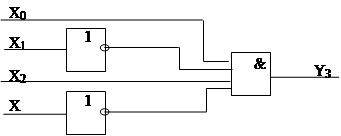

2.2.3 Синтез блока контроля заданных комбинаций на логических элементах

Для синтеза блока контроля заданных комбинаций на логических элементах, в которой выходная функция Yз

приравнивается к значению «лог. 1» на заданной выходной комбинации переменных генератора кодов X3

X2

X1

X0

-0101, и значение «лог. 0» на всех остальных наборах. Далее запишем саму функцию , затем реализуем ее на схеме.

Рис. 2.6. Блок контроля заданной комбинации на логических элементах

2.2.4 Синтез блока контроля заданных комбинаций на мультиплексорах

Для построения блока контроля заданных комбинаций на мультиплексоре необходимо в таблицу истинности напротив заданной комбинации в столбце функции поставить «1», а остальные – «0», полученная таблица представлена в таб. 2.5.

Таблица 2.5

| X3

|

X2

|

X1

|

X0

|

Yз

|

№ входа |

информация |

| 0 |

0 |

0 |

0 |

0 |

D0 |

0 |

| 0 |

0 |

0 |

1 |

0 |

| 0 |

0 |

1 |

0 |

0 |

D1 |

0 |

| 0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

0 |

0 |

D2 |

X0

|

| 0 |

1 |

0 |

1 |

1 |

| 0 |

1 |

1 |

0 |

0 |

D3 |

0 |

| 0 |

1 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

0 |

D4 |

0 |

| 1 |

0 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

0 |

D5 |

0 |

| 1 |

0 |

1 |

1 |

0 |

| 1 |

1 |

0 |

0 |

0 |

D6 |

0 |

| 1 |

1 |

0 |

1 |

0 |

| 1 |

1 |

1 |

0 |

0 |

D7 |

0 |

| 1 |

1 |

1 |

1 |

0 |

Рис. 2.7. Блок контроля заданной комбинации на мультиплексорах

2.3 Сравнительный анализ и выбор оптимального варианта функциональной схемы

Критерием оптимизации при выборе варианта схемы проектируемого устройства согласно заданию выступает минимум затрат аппаратуры. Для того, чтобы сравнить рассмотренные выше варианты реализации схемы по этому критерию, составим сводную таблицу потребного количества корпусов микросхем для каждого блока, для составления таблицы условно принято, что в одном корпусе микросхемы может содержаться несколько логических элементов, один функциональный четырехразрядный узел (к примеру, мультиплексор). Полученная таблица представлена ниже (таб. 2.6).

Таблица 2.6

| Блок |

Вариант |

Элемент |

Количество элементов |

Количество корпусов ИС |

| Генератор кодов |

Счетчик + комбинационная схема на логических элементах |

Счетчик СТ10 |

1 |

1 |

| НЕ |

3 |

1 |

| И(2вх) |

6 |

2 |

| И(3вх) |

2 |

1 |

| ИЛИ(2вх) |

1 |

1 |

| ИЛИ(3вх) |

2 |

1 |

| ИЛИ(4вх) |

1 |

1 |

| Итого |

8 |

| Счетчик + комбинационная схема на мультиплексорах |

Счетчик СТ10 |

1 |

1 |

| НЕ |

1 |

1 |

| MUX |

4 |

4 |

| Итого |

6 |

| Блок контроля ошибочных комбинаций |

На логических элементах |

НЕ |

3 |

1 |

| И(2вх) |

3 |

1 |

| ИЛИ(3вх) |

1 |

1 |

| Итого |

3 |

| На мультиплексорах |

MUX |

1 |

1 |

| Итого |

1 |

| Блок контроля заданных комбинаций |

На логических элементах |

НЕ |

2 |

1 |

| И(4вх) |

1 |

1 |

| Итого |

2 |

| На мультиплексорах |

MUX |

1 |

1 |

| Итого |

1 |

Проанализировав полученную таблицу можно сделать вывод, что генератор кодов, блок контроля ошибочных комбинаций и блок контроля заданных комбинаций целесообразнее проектировать на мультиплексорах, так как это приведет к минимуму аппаратных затрат.

3. Разработка принципиальной схемы

3.1 Выбор элементной базы

При выборе элементной базы вычислительного устройства следует руководствоваться комплексом показателей от быстродействия до конструктивно-технологического исполнения элементов. Исходными данными для обоснованного выбора элементов являются требования задания, где оговорены:

-тактовая частота генератора кодов (20±1)МГц;

-напряжение питания (5±0,25)B;

-условия эксплуатации.

Заданному диапазону температур данная элементная база удовлетворяет.

Таблица 3.1

| Параметры |

ТТЛ |

ТТЛШ |

ЭСЛ |

КМДП |

| Среднее время задержки сигнала tср

, нс |

10¸30 |

5¸20 |

0,5¸2 |

15¸50 |

| Частота переключения Fmax

, МГц |

15 |

25

¸

100

|

300

|

5 |

| Статические помехи, В |

0,4 |

0,4 |

0,125 |

0,3 |

| Напряжение питания Епит

, В |

5

|

5

|

-5,2 |

3

¸

15

|

Как видно из таблицы 3.1, что по питающему напряжению, условиям эксплуатации отвечают ИС: ТТЛ, ТТЛШ и КМДП. По частоте переключения условиям отвечают ТТЛШ и ЭСЛ. Поэтому для построения устройства выбираем элементы ТТЛШ, так как подходят под заданные условия эксплуатации по большим признакам (по двум), чем остальные элементы. Существует множество серий элементов ТТЛШ, например, К555, К1531, К1533, К155, К561 и т.д., отличающихся друг от друга значением различных характеристик. Для обеспечения нормальной работы устройства, с заданной частотой выработки импульсов, необходимо взять следующие типы микросхем: логический элемент И-НЕ – К555ЛА3, двоично-десятичный счетчик СТ10 – К1533ИЕ6, логический элемент НЕ – К1531ЛН1, мультиплексор MUX – К1531КП7.

3.2 Выбор схемы и расчет генератора тактовых импульсов

В зависимости от назначения и предъявляемых требований генератор тактовых импульсов можно выполнить на дискретных компонентах или на основе специализированной интегральной схемы.

Предпочтительным следует признать вариант исполнения генератора тактовых импульсов на основе логических микросхем, схема генератора тактовых импульсов при этом отличается простотой, надежностью и естественным сопряжением с выбранной системой цифровых элементов. Хотя в схеме и не достигается особая стабильность частоты импульсов, она в генераторе кодов и не требуется.

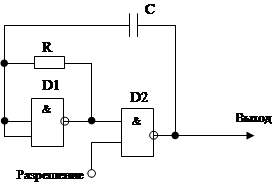

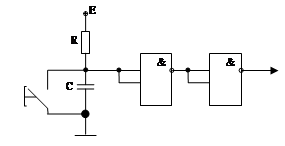

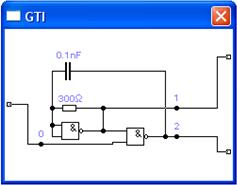

Рис. 3.1. Генератор тактовых импульсов на логических элементах

На рисунке 3.1 представлен вариант распространенной схемы ТТЛ автогенератора на логических элементах. В этой схеме инвертор D1 служит компаратором с порогом переключения порядка 1,4 В, а конъюнктор D2 обеспечивает общую положительную обратную связь в устройстве через конденсатор С, попутно решая задачу запуска и останова генерирования. Генератор вырабатывает импульсы с уровнями ТТЛШ типа «меандр» с равными длительностями полуволн и частотой

, ,

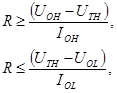

причем сопротивление резистора R должно удовлетворять двум условиям:

где:UOH

– выходное напряжение высокого уровня;

UTH

– порог переключения;

IOH

– выходной ток высокого уровня;

IО

L

– выходной ток низкого уровня.

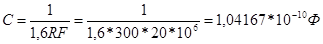

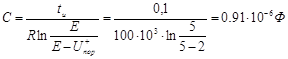

На практике в зависимости от используемых ИС сопротивление R выбирают в пределах 200…400 Ом. Возьмем R=300 Ом, частота задана по заданию F=20 МГц, следовательно можно найти С, по описанной ранее формуле:

Выберем конденсатор типа К10-17 с ближайшим номиналом С равным 0,1нФ или 100пФ.

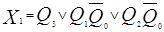

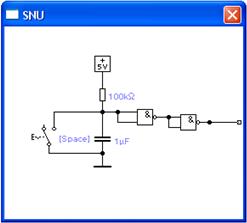

3.3 Расчет схемы начальной установки

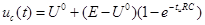

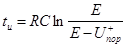

Схема начальной установки (СНУ) предназначена для установки устройства в исходное состояние при включении питания, т.е. формирование единственного импульса для сброса последовательностных узлов. Длительность формируемого импульса должна быть, во всяком случае, больше времени установления питающего напряжения при его включении. Пусть импульс равен 0,1 с. Для того, чтобы исключить дребезг по фронтам импульса, построим СНУ на основе логических элементов.

Рис. 3.2. Схема начальной установки

При включении питания Е на конденсаторе С согласно закону коммутации вначале удерживается напряжение, близкое к нулю, а затем возникает процесс его заряда через резистор R в соответствии с выражением:

При  следует: следует:

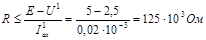

Сопротивление резистора R выбирается таким, чтобы в статике обеспечивался высокий логический уровень на входе, т.е.

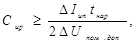

Выбрав номинал R равным 100 кОм, найдем необходимое значение емкости С:

Большинство конденсаторов такой емкости выпускаются по ряду Е12, поэтому выберем ближайший номинал С равным 1 мкФ.

3.4 Расчет конденсаторов развязки по цепи питания

Идея применения конденсаторов развязки для уменьшения импульсных помех заключается в уменьшении эквивалентной паразитной индуктивности шин питания (5V) и земли (0V) путем создания индивидуального источника энергии для обеспечения тока потребления в момент переключения микросхем. Обычно применяют индивидуальные конденсаторы развязки керамического типа для устранения помех из-за «быстрых» бросков тока в цепи питания, которые устанавливаются рядом с каждой микросхемой, и групповые конденсаторы развязки электролитического типа для исключения «медленных» колебаний питающего напряжения. Емкость конденсатора индивидуальной развязки выбирают из условия:

где:∆Iun

- максимальное значение переменной составляющей тока потребления; tнар

- длительность импульса тока; ∆Uпом.доп

- допустимое значение импульсной помехи.

В качестве ∆Iun

берут, как правило, 1/3 от значения тока короткого замыкания Iкз

по выходу микросхемы, который для микросхем серии К555 можно найти как:

где:Е

= 5 В - напряжение питания; Uкэ

= 0,95В

- напряжение коллектор-эмиттер выходного насыщенного транзистора в микросхеме; Rогр

= 200 0м

- сопротивление токоограничительного резистора в микросхеме.

Тогда следует, что:

Выберем конденсаторы индивидуальной развязки типа К10-17, а их номинал С

up

равным 0,01 мкФ.

Емкость конденсатора групповой развязки выбирается из условия:

где Lш

и Rш

- соответственно индуктивность и сопротивление шины питания. Так как конструкция устройства в рамках курсового проекта не разрабатывается, то указанные параметры не могут быть определены точно. По этой причине емкость С

р

возьмем равной 1 мкФ, как это обычно и принимается в практических устройствах на двухслойных печатных платах.

3.5 Расчет длительности переходных процессов

Длительность переходных процессов от момента выработки очередного тактового импульса до момента установления нового состояния устройства определяется с целью оценки быстродействия устройства и для выявления сбойных ситуаций, когда сигнал в цепи обратной связи (при наличии таковой) не успевает поступить на вход устройства до момента выработки следующего тактового импульса.

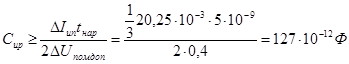

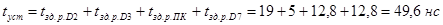

В разрабатываемом устройстве представляет интерес время распространения сигнала от ГТИ до момента записи кода. Цепь распространения информации при этом включает:

счетчик D2 (К1533ИЕ6) - время задержки распространения сигнала от тактового входа до информационных выходов составляет: tзд.р

D

2

=19нс;

время задержки распространения сигнала в логическом элементе D3 (К1531ЛН1) составляет: tзд.р

D

3

=5нс;

преобразователь кодов на мультиплексорах D4..D7 (К1531КП7) от адресных входов до информационных выходов - время задержки распространения сигнала составляет: tзд.рПК

=12,8нс;

блок контроля кодовых комбинаций D8 от информационных входов до выхода – время задержки распространения сигнала составляет: tзд.р

D

8

=12,8нс;

Общее время переходного процесса в первом цикле работы, таким образом, составляет

Таким образом, при заданной тактовой частоте (F=20МГц) обеспечивается устойчивое функционирование устройства, т.к. tуст

. меньше тактового периода (49,6<50).

3.6 Расчет потребляемой мощности

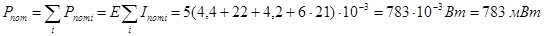

Мощность, рассеиваемая в процессе работы устройства, складывается из мощностей, потребляемых входящими в него элементами:

3.7 Оценка показателей надежности

Основными показателями надежности устройства служат вероятность безотказной работы P(t), вероятность неисправной работы Q(t),

наработка на отказ T0

и коэффициент готовности Кг

.

Исходными данными для расчета этих показателей служат значения интенсивности отказов λi

для каждого входящего в устройство элемента. Взятые из справочников значения λi

приведены в таблице 3.2.

Таблица 3.2

| Тип элемента |

Количество |

Значение λ |

| Конденсатор К53-14 |

1 |

0,035×10-6

|

| Конденсатор К 10-17 |

11 |

0,03×10-6

|

| Резистор С2-33 |

3 |

0,05×10-6

|

| Микросхема К555ЛА3 |

1 |

0,01824×10-6

|

| Микросхема К1531ЛН1 |

1 |

0,01824×10-6

|

| Микросхема К1531КП7 |

6 |

0,0228×10-6

|

| МикросхемаК1533ИЕ6 |

1 |

0,0228×10-6

|

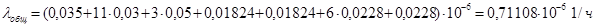

Общая интенсивность отказов определяется формулой:

и будет равна:

Значение λобщ

определено для лабораторных условий эксплуатации и для наземных стационарных условий должно быть скорректировано умножением на поправочный коэффициент К = 10.

Таким образом, при расчете будем считать λобщ

= 0,71108×10-6

1/ час.

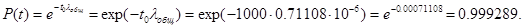

Определим вероятность безотказной работы устройства в течение 1000

час:

Тогда вероятность неисправной работы будет равна:

Q(t) = 1- P(t) = 1- 0,989953 = 0,00071083.

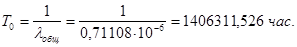

Наработка на отказ составит:

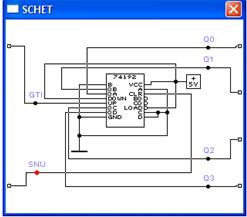

Значение коэффициента готовности зависит от времени ремонта данного устройства Тр

,

которое для простого устройства не превышает 0,5 час. Тогда коэффициент готовности будет равен:

полученное значение коэффициента готовности следует признать удовлетворительным.

4. Моделирование отдельных узлов генератора в программе «

Electronics

Workbench»

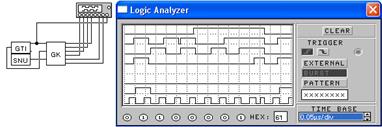

Моделирование схемы проводится с целью практической апробации результатов проектирования и подтверждения работоспособности устройства. Для моделирования используется программа «Electronics Workbench», совмещающая возможности анализа и проектирования схем. Для проверки работоспособности спроектируем и проанализируем работу блока генератор кодов. На рисунках представленных ниже приведены модели отдельных блоков генератора и модель самого генератора кодов.

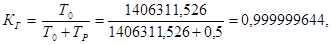

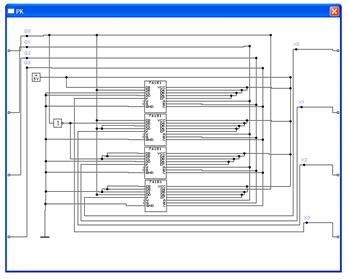

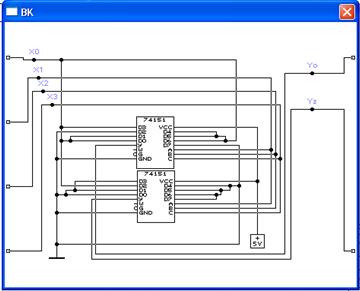

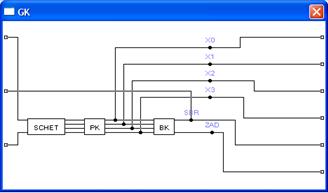

Рис. 4.1 – блок преобразователя кодов «РК», рис. 4.2 – блок контроля «ВК», рис. 4.3 – схема счетчика упрощенная «SCHET», рис. 4.4 – блок генератора кодов «GK», рис. 4.5 – блок генератора тактовых импульсов «GTI», рис. 4.6 – блок схемы начальной установки «SNU», рис. 4.7 – собранная схема генератора кодов и сигналограмма его работы.

Рис. 4.1. Схема преобразователя кодов «РК»

Рис. 4.2. Блок контроля «ВК»

Рис. 4.3. Схема счетчика упрощенная «SCHET»

Рис. 4.4 – блок генератора кодов «GK»

Рис. 4.5 – блок генератора тактовых импульсов «GTI»

Рис. 4.6 – блок схемы начальной установки «SNU»

Рис. 4.7 – схема генератора кодов и сигналограмма

Как следует из полученных временных диаграмм сигналов на выходах ГК (рис.4.7), он циклически (начало цикла соответствует нижней диаграмме импульса переноса счётчика импульсов) принимает состояния: 0000, 0101, 0010, 0100, 0110, 1000, 1010, 1100, 1110, 1111, Перечисленные стояния соответствуют заданной последовательности кодов. На рис.4.7 проиллюстрирован процесс выявления незапланированных кодов блоком контроля (3-я диаграмма снизу на сигналограмме), что позволяет судить о правильности работы устройства, так как сигнал на выходе блока контроля находится в состоянии «0», т.е. устройство не выдает ошибки, следовательно, устройство не дает сбоев и выдает заданные кодовые последовательности.

Заключение

Разработанный генератор кодовых последовательностей импульсов рассчитан на работу в стационарных наземных условиях и полностью соответствует заданию. В рамках проекта рассмотрены варианты реализации узлов и компонентов устройства, путем сравнительного анализа выбран оптимальный вариант схемы, проверена работоспособность схемы. Определены основные показатели функционирования и оценена надежность устройства.

Генератор кодовых последовательностей импульсов построен на базе стандартных интегральных микросхем преимущественно типа ТТЛШ и может найти применение в качестве контроллера вычислительной информационной системы.

Литература

1. Схемотехника ЭВМ: Учебник для студентов вузов спец. ЭВМ. Под ред. Г.Н. Соловьева. - М.: Высшая школа, 1985.

2. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ: Учебное пособие для спец. ЭВМ вузов. - М.: Высшая школа,1987.

3. Алексенко А.Г., Шагурин И.И. Микросхемотехника: Учеб. пособие для вузов.- М.:Радио и связь, 1990.

4. Последовательностные схемы средней интеграции типа транзисторно-транзисторной логики: Описание лабораторных работ по курсу «Расчет и проектирование элементов ЭВМ»./ Лернер М.И., Трифонов Е.Ф., Шадрин М.п. - Пенза, РИО ППИ, 1985.

5. Цифровые интегральные микросхемы: Справочник/ М.И.Богданович, И.Н.Грель, С.А.Дубина и др. - Мн.: Беларусь, Полымя, 1996.

6. Применение интегральных микросхем памяти: Справочник/А.А. Дерюгин, В.В. Цыркин, В.Е. Красовский и др.; Под ред. А.Ю. Гордонова, А.А. Дерюгина.- М.: Радио и связь, 1994.

7. Справочник разработчика и конструктора РЭА. Элементная база. - М.: ИТАР-ТАСС, 1993.

8. Шило В.Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. - М.: Сов. радио, 1979.

9. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств: Учеб. пособие / Под ред. Л.Н.Преснухина. - М.: Высшая школа, 1982.

10. Схемотехника ЭВМ: Методические указания по курсовому проектированию./Лернер М.И., Смирнов А.М., Шадрин М.П., Трифонов Е.Ф. - Пенза, РИО ППИ, 1986.

11. Чулков В.А., Смагин Ю.А., Фролов Г.В. Компьютерное макетирование электронных схем: Методическое пособие. - Пенза, Изд-во Пензенского технологического института, 1999.

|