| Содержание

Введение

Устройство и технические данные промышленного робота СМ40Ц

Описание технологического процесса

Описание микропроцессорного комплекта серии U83-K1883

Система команд микропроцессорного комплекта U83-K1883

Описание микросхемы К572ПВ4

Описание функциональной схемы управления

Описание принципиальной схемы

Описание алгоритма работы программы управления

Управляющая программа

Расчет надежности

Список используемой литературы

Введение

В последнее время все большую актуальность стали приобретать процессы автоматизации всего технического оборудования, применяемого в станках, машинах и механизмах, робототехнических комплексах. Благодаря внедрению в производство новых технологий, существенно повышается производительность труда, причем доля ручного труда по сравнению с автоматизированным значительно уменьшается. Повышается технический уровень выпускаемой продукции, существенно улучшается ее качество. Все это, наверное, невозможно было бы осуществить без микропроцессорных вычислительных средств. Приборы, которые выполнены с применением микропроцессоров, имеют более высокие показатели в работе по сравнению с приборами, выполненными на отдельных логических схемах, причем стоимость первых значительно меньше.

Микропроцессор представляет собой автономное функционально законченное устройство, состоящее из одной или нескольких программно управляемых БИС, включающее все средства. Необходимые для обработки информации и управления данными, и рассчитанное на совместную работу с устройствами памяти и ввода/вывода информации.

В данной работе представлена разработка микропроцессорной системе управления на основе микропроцессорного комплекта 1883 роботом СМ40Ц.

Устройство и технические данные промышленного робота СМ40Ц

Рис. 1. Внешний вид промышленного робота СМ40Ц

Промышленный робот СМ40Ц40.11 предназначен для обслуживания металлорежущих станков с горизонтальной осью вращения в составе роботизированных технологических комплексов и обеспечивает загрузку станков заготовками типа валов и фланцев и их разгрузку.

Рис. 2. Кинематическая схема промышленного робота СМ40Ц

Технические данные:

· модель робота СМ40Ц40.11

Реклама

· грузоподъемность 40 кг;

· число степеней подвижности 4;

· привод основных движений гидравлический;

· погрешность позиционирования 1,5 мм;

· линейное перемещение  760 мм, 0,5 м/с; 760 мм, 0,5 м/с;

· линейное перемещение  760 мм, 0,2 м/с; 760 мм, 0,2 м/с;

· угловое перемещение  240 град, 60 град/с; 240 град, 60 град/с;

· угловое перемещение  180 град, 90 град/с; 180 град, 90 град/с;

· масса 1400 кг

Описание технологического процесса

Рис. 3. Роботизированный технологический комплекс на базе станка с ЧПУ; 1 – станок с ЧПУ, 2 – робот, 3 – конвейер с заготовками, 4 – конвейер с деталями

В начале цикла робот 2 берет заготовку с конвейера 3, затем переносит ее к металлорежущему станку 1 и устанавливает. После того как деталь будет обработана, робот берет ее и кладет на конвейер 4. Цикл повторяется до тех пор, пока не будет изготовлено необходимое количество деталей.

Описание микропроцессорного комплекта серии U83-K1883

МПК серии U83-K1883, разработка которого проводилась специалистами СССР и ГДР, выполнен на базе n-МДП-технологии и предназначен для построения процессоров микро- и мини-ЭВМ, контроллеров и других вычислительных устройств среднего быстродействия. Этот МПК принадлежит к группе секционированных микропроцессоров с микропрограммным управлением, что позволяет строить на его основе вычислительные устройства с длиной обрабатываемых чисел 8, 16 или 32 разряда.

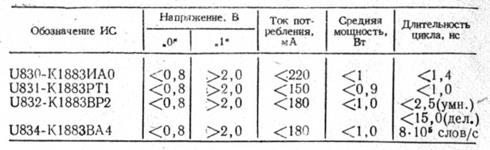

В состав МПК U83-K1883 входят четыре микросхемы высокой степени интеграции, выполненные в керамических корпусах с 48 выводами; МПК следует использовать в диапазоне температур от О до 70°С (в нерабочем состоянии от — 60 до 125° С). Питание всех схем МПК осуществляется от одного источника (+5 В ±5%), их электрические параметры приведены в табл. 1.

Таблица 1

В состав комплекта входят БИС арифметического устройства, управляющей памяти, арифметического расширителя и магистрального адаптера.

Арифметическое устройство

(АУ) U830-K1883ИA0 представляет собой 8-разрядную процессорную секцию, выполняющую сложение, вычитание, логические операции И, ИЛИ, ИЛИ—ИЛИ, перенос, сдвиг, дополнение и т.д. Назначение выводов корпуса БИС АУ приведено в табл. 2.

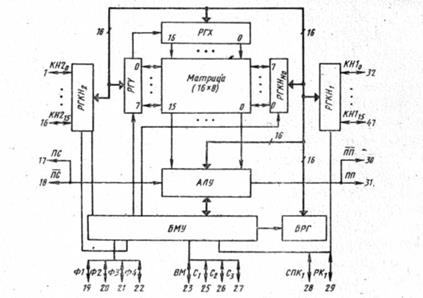

В состав БИС АУ U830-K1883ИAO входят: арифметико-логическое устройство (АЛУ), регистр и дешифратор микрокоманд (РМК и ДШ), блок местного управления (БМУ), блок регистров (БРГ), блок расширения (БРШ), блок формирования флагов (БФФ), три блока усилителей каналов 1, 2, 3, блок управления каналами и регистр состояний (рис. 4).

Арифметико-логическое устройство выполняет обработку 8-разрядных данных, поступающих по шинам X и У на два входных регистра. Блок регистров содержит 18 свободно адресуемых 8-разрядных регистров R00-R15, А1, А2, предназначенных для приема операндов и результатов обработки. Регистр А2, кроме того, служит для хранения флагов N, Z, V, С. Регистр микрокоманд и дешифратор служат для приема поступающей на схему микрокоманды, ее дешифровки и выработки последовательности управляющих импульсов.

Реклама

Каналы 1 и 2 предназначены для приема и передачи данных. Блок управления каналами управляет приемом и передачей данных по ним. Канал 3 служит для выдачи содержимого флагового регистра А2 или блока формирования флага.

Блок расширения предназначен для объединения до четырех схем АУ с целью расширения разрядности обрабатываемых данных. 4-разрядный регистр состояний может быть загружен микрокомандами обработки операндов или микрокомандами управления каналами. Вся схема синхронизируется блоком местного управления.

Работа схемы происходит по асинхронному принципу. На входы кода микрокоманды (МК.) поступает 14-разрядный код микрокоманды, считанный из схемы управляющей памяти. После ее дешифрации формируется совокупность сигналов, которые поступают на те блоки схемы, которые обеспечивают выполнение данной микрокоманды. АЛУ производит обработку данных, поступающих по одинаковым по значимости каналам 1 и 2 или хранящихся в регистрах R00—R15, А1, А2 и в регистре состояний. Результат операции поступает на один из регистров или на один из каналов.

Рис. 4. Структурная схема БИС арифметического устройства U830-K1883ИA0

Таблица 2

Сигналы сопровождения данных (СПД), приема данных по каналу (ПМК), разрешения выдачи (РВД), синхронизации канала входа (С) и выбора микросхемы (ВМ) служат для синхронизации работы схемы и для разрешения ввода и вывода данных. Кроме того сигнал ВЫБОР МИКРОСХЕМЫ служит для выбора прибора. Через вход БЛКН может быть подана команда о прямом обращении к памяти. Входы СД1—СД4 предназначены для объединения схем АУ для обработки многоразрядных слов (16, 24, 32 разряда). Содержание флагового регистра блока формирования флага может быть выдано по каналу 3.

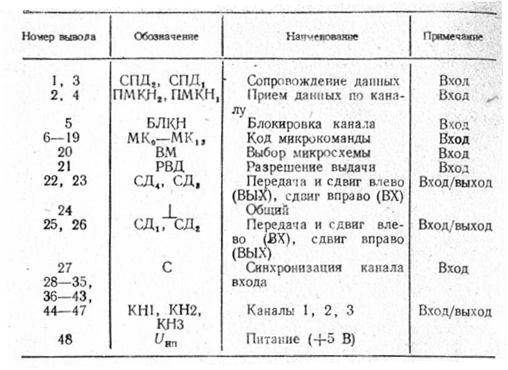

БИС управляющей памяти

(УП) U831-К1883РТ1 предназначена для организации вычислительного процесса путем преобразования машинных команд в последовательности микрокоманд, необходимых для управления БИС АУ U830-К1883ИА0 и БИС АР U832-K1883BP2. Кроме того, БИС УП может быть использована в качестве кодирующего и декодирующего преобразователя. Назначение выводов корпуса БИС УП приведено в табл. 3.

В состав УП (рис. 5) входят: программируемая логическая матрица, блок синхронизации и регистры различного назначения.

Программируемая логическая матрица (ПЛМ) состоит из матрицы 1, содержащей 140 логических схем НЕ—ИЛИ и имеющей 56 входов, и матрицы 2, содержащей 34 логические схемы НЕ—ИЛИ и имеющей 140 входов и 34 выхода. В данной ПЛМ машинная команда может быть приведена к последовательности микрокоманд, число которых может достигать 256. На выходе ПЛМ размещен регистр чтения (РГЧТ), с которого информация через блок программируемых инверторов (БПИ) подается либо на регистр следующего адреса, либо на управляющий регистр (РГУ), либо на выходной регистр (РГВЫХ). 8-разрядный регистр следующего адреса предназначен для организации необходимой последовательности микрокоманд на выходе БИС УП. 8-разрядный управляющий регистр используется для внутренней синхронизации работы схемы. Выходной регистр и блок выходных усилителей (УСВЫХ) предназначен для временного хранения информации и выдачи ее на схемы, которые управляются от БИС УП.

Рис. 5. Структурная схема БИС управляющей памяти U831-К1883РТ1

Таблица 3

Режим работы БИС УП (т.е. список микрокоманд, вырабатываемых ПЛМ) задается изготовителем схемы путем программирования связей внутри ПЛМ в соответствии с назначением. Поэтому может быть несколько модификаций БИС УП, отличающихся лишь записанной в них информацией.

Асинхронный режим работы БИС УП позволяет использовать ее для организации медленно протекающих операций, что позволяет исключить необходимые для этого схемы задержки, ожидания и согласования. Возможно применение нескольких БИС УП для управления процессом, причем каждая БИС может управлять частью процесса.

Арифметический расширитель

(БИС АР) U832-K1883BP2 предназначен для аппаратного выполнения основных арифметических операций над числами с фиксированной и плавающей запятой. Включение этой схемы в состав МПК U83-K1883 позволяет увеличить быстродействие построенных на нем вычислительных устройств. В одной схеме БИС АР производятся операции над числами с разрядностью 16 бит. Включая две или четыре БИС АР, можно обрабатывать числа с разрядностью 32 или 64 бита.

БИС АР выполняет следующие функции:

сложение, вычитание, умножение, деление, умножение с последующим сложением двух чисел с фиксированной и плавающей запятой;

преобразование чисел с фиксированной запятой в числа с плавающей запятой и обратно;

сравнение, сдвиг, поиск разрядов.

Наличие внутреннего управления, работа схемы по поступлению одной внешней соответствующей микрокоманды, сравнительно короткое время выполнения операций, асинхронный режим работы и т. д. позволяют использовать БИС АР не только в традиционных вычислительных устройствах, но и в дискретных фильтрах, полиномиальных процессорах, различной бытовой аппаратуре.

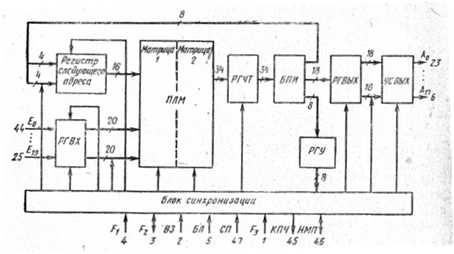

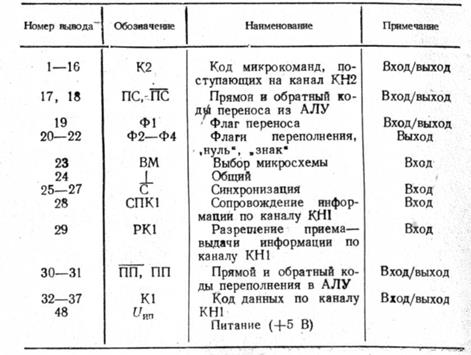

БИС АР выполнена в 48-выводном корпусе, назначение которых приведено в табл. 4. Структурная схема БИС АР приведена на рис. 6. В состав БИС АР входят: матрица с регистрами РГХ, РГУ и РГИ, АЛУ, блок регистров (БРГ), два канальных регистра (РГК1 и РГК2) и блок местного управления (БМУ).

Рис. 6. Структурная схема БИС арифметического расширителя U832-K1883BP2

Таблица 4

Матрица, представляющая собой поле из 16X8 сумматоров, соединенных по схеме умножения, предназначена для выполнения операции умножения 16-разрядного операнда, поступающего на регистр РГХ, и 8-разрядного операнда, поступающего на РГУ. Результат умножения размещается в регистре РГИ или поступает на вход АЛУ. АЛУ выполняет арифметические и логические операции, код которых поступает по каналу К2 на регистр РГК2. Прием операндов и выдача результатов осуществляется по каналу К1 через РГК1.

Восемь 16-разрядных регистров (БРГ) используются как внутренняя память БИС АР. Блок местного управления осуществляет управление работой схемы при поступлении на него различных условий. Обмен данными между узлами БИС АР осуществляется с помощью 16-разрядной шины.

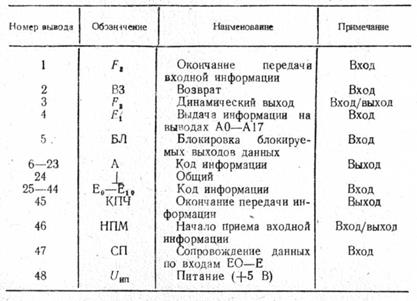

Магистральный адаптер

(MA) U834-K1883BA4 предназначен для осуществления аппаратной связи между внешними устройствами (в том числе объектами управления) и процессором ЭВМ.

Рис. 7. Структурная схема БИС магистрального адаптера U834-K1883BA3

МА выполняет следующие функции:

связь между шиной МП и шиной внешних устройств;

управление передачей данных из МП во внешние устройства и обратно;

управление режимом прямого обращения к памяти;

организацию режима прерываний при работе с внешними устройствами и памятью.

БИС МА размещена в корпусе из 48 выводов, назначение каждого приведено в табл. 5. Структурная схема БИС МА приведена на рис. 7. МА включает в себя блок регистров (БРГ), блок местного управления (БМУ), блок управления прерываниями (БУПР), блок прямого доступа к памяти (БПДП) и блок приемопередатчиков адресов и данных (БППДА). БМУ осуществляет внутреннюю синхронизацию БИС МА, управляя работой как отдельных блоков, так и внутренней шины.

Система команд микропроцессорного комплекта U83-K1883

Группа команд пересылки данных используется для организации операции загрузки, хранения и межрегистровых передач данных. Наиболее часто применяют команды типа MOV (передача данных), XCH (обмен содержимого), OUT (вывод данных), IN (ввод данных). Команда MOV r1, r2 осуществляет пересылку информации из регистра r2 в регистр r1. В качестве регистра – источника и регистра – приемника может выступать и аккумулятор. Команды типа MOV иногда могут адресоваться и к ячейкам памяти, при этом адрес ячейки, как правило, хранится в одном из регистров ЦП.

К командам, выполняющим преобразования данных, относятся:

ANL – логическая операция И;

ORL – логическая операция ИЛИ;

XRL – операция исключения ИЛИ;

RR – циклический сдвиг вправо;

RL – циклический сдвиг влево;

INC – инкрементирование;

DEC – декрементирование;

ADD – сложение;

SUB – вычитание;

CMP – сравнение.

Таблица 5

К командам управления относятся команды типа: STOP – останов таймера/счетчика событий, JMP – безусловный переход и ряд команд условного перехода, таких, как JE, JA, JB, JAE, JBE, JNE.

JE – переход если равно;

JA – переход если больше;

JB – переход если меньше;

JAE – переход если больше или равно;

JBE – переход если меньше или равно;

JNE - переход если не равно.

При необходимости произвести требуемые вычисления осуществляется вызов подпрограммы, она исполняется, после чего производится возврат в основную программу. Эти операции реализуются с помощью команд типа CALL (вызов) и RET.

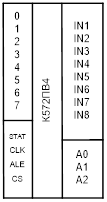

Описание микросхемы К572ПВ4

Микросхема К572ПВ4 - аналого-цифровой системы (АЦС) сбора данных (рис. 8) предназначена для преобразования аналоговых сигналов, поступающих по восьми параллельным каналам в цифровой код с последующим его сохранением в ОЗУ и считыванием во внешнем МП в режиме прямого доступа к памяти. Микросхема АЦС К572ПВ4 изготовлена по КМОП технологии.

Система сбора данных обеспечивает непосредственное сопряжение с МП, имеющими как раздельные, так и общие шины адреса и данных. Управление К572ПВ4 осуществляется от МП логическими сигналами ТТЛ и КМОП уровней. Режим прямого доступа к памяти реализуется в соответствии с алгоритмом последовательной обработки аналоговых сигналов по восьми независимым входам.

Рис. 8. Условное графическое обозначение микросхемы К572ПВ4

Назначение выводов:

0 – 7 – цифровые выхода;

STAT – выбор канала и начало преобразования;

CS – вход управления считыванием данных ОЗУ;

CLK – вход тактовых импульсов;

ALE – вход управления при обращении к ОЗУ;

А0 – А2 – адресные входы;

IN1 – IN8 – входы мультиплексора.

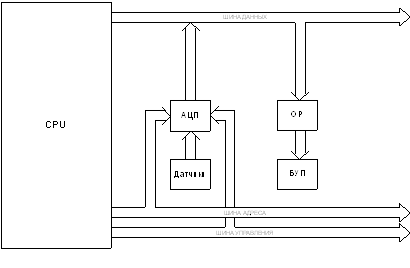

Описание функциональной схемы управления

Основу микропроцессорной системы управления технологическим оборудованием (рис. 9) составляет микропроцессор (CPU) серии U83-К1883. Он осуществляет управление всеми микросхемами, входящими в устройство, производит ввод информации с датчиков и выполняет её обработку по заданному алгоритму. После чего выдает определенные сигналы управления, в результате которых производится включение или выключение исполнительных приводов. Ввод информации с датчиков и вывод сигналов управления на приводы осуществляется по шине данных, разделенной на шину ввода и шину вывода, к которым соответственно подключены АЦП с коммутатором и оптронные развязки (ОР) с блоком управления приводами (БУП). Оптронные развязки предназначены для электрической развязки управляющей аппаратуры и исполнительных приводов. Данная развязка делается для того, чтобы при выходе из строя исполнительного элемента управляющая аппаратура не вышла из строя. В связи с тем, что в системе используется аналоговые датчики, а устройство управления работает с цифровыми сигналами, в неё введен аналого-цифровой преобразователь (АЦП) с коммутатором, который выполняет преобразование аналогового сигнала с выбранного датчика в цифровую форму.

Рис. 9. Функциональная схема системы управления

Описание принципиальной схемы

Основными частями микропроцессорного устройства управления являются три микросхемы: БИС управляющей памяти, БИС арифметического устройства, аналогово-цифровой преобразователь (АЦП). ЦП выполняет основную роль (рис. 10), т.к. по его сигналам управления производится запуск АЦП, считывание информации с датчиков, которая в дальнейшем обрабатывается в ЦП по определенному алгоритму, и в зависимости от результата производится формирование и выдачу управляющих сигналов для того или иного привода.

При необходимости считывания информации с датчика, микропроцессор на шину адреса выдает информацию, которая указывает, с какого датчика будет производиться считывание информации. После этого микропроцессор формирует сигналы управления, которые указывают микросхемам на то, что процесс считывания должен быть начат и производить ввод информации с шины данных.

При необходимости включения привода, ЦП передает цифровой код, который указывает, как и какой привод будет работать. Далее через оптронную развязку сигнал поступает на блок управления приводами.

DD1 – БИС управляющей памяти U831-К1883РТ1;

DD2 – БИС арифметического устройства U830-K1883ИA0;

DD3 – восьмиразрядный аналогово-цифровой преобразователь К572ПВ4; BL1 –BL5 – оптронная развязка.

Описание алгоритма работы программы управления

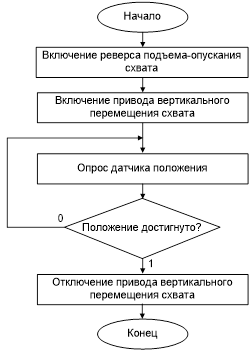

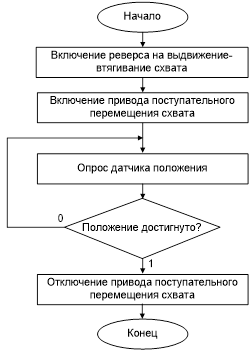

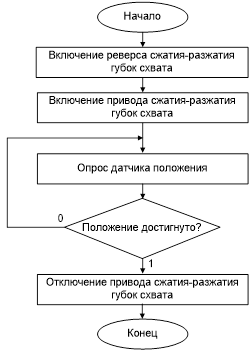

В начале работы программы происходит опрос датчиков на определение положения схвата. Если схват не находится в начальном положении, то с помощью приводов схват переводится в начальное положение. Далее происходит опрос датчиков на наличие заготовки в накопителе, если заготовки нет, то робот ждет, пока она не появится (задержка времени). Затем идет обращение к подпрограмме выдвижения (втягивания) схвата и сжатия (разжатия) губок - робот берет заготовку. Затем происходит перемещение схвата к станку путем вызова ряда подпрограмм: выдвижение (втягивание) схвата, поворот звена, опускание (поднятие) схвата, выдвижение (втягивание) схвата, сжатие (разжатие) губок, выдвижение (втягивание) схвата - заготовка устанавливается в станок. При этом, в момент работы подпрограммы, считывается информация с соответствующего датчика, и если схват достиг нужного положения, то происходит отключение привода и выполняется следующая подпрограмма.

Происходит процесс обработки заготовки, робот ожидает окончания процесса. По его окончанию, изделие изымается из станка (выполняются подпрограммы выдвижения (втягивания) схвата, сжатия (разжатия) схвата, выдвижения (втягивания) схвата) и помещается на конвейер (подпрограммы поворота схвата, выдвижения (втягивания), опускание (поднятие) и сжатия (разжатия) губок схвта), а робот возвращается в исходное положение.

Если на этом технологический процесс окончен, то конец программы, если нет, то робот снова приступает к вышеописанным операциям (рис. 11, 12).

Рис. 11. Алгоритм работы программы управления

а) подпрограмма подъема (опускания) схвата

б) подпрограмма выдвижения (втягивания) схвата

в) подпрограмма сжатия (разжатия) губок схвата

г) подпрограмма поворота схвата

Рис. 12. Алгоритмы работы подпрограмм программы управления

Управляющая программа

D1 – датчик положения манипулятора при горизонтальном перемещении, D2 – датчик положения манипулятора при вертикальном перемещении, D3 – датчик поворота схвата, D4 – датчик сжатия-разжатия губок схвата, D5 – датчик наличия заготовки в накопителе, D6 – датчик окончания процесса обработки заготовки, D7 - датчик окончания технологического процесса

REV - реверс

DV1 – привод горизонтального перемещения манипулятора

DV2 – привод вертикального перемещения манипулятора

DV3 – привод поворота схвата

DV4 – привод сжатия-разжатия губок схвата

N0, N1, N2 – ячейки памяти, в которых хранятся величины поворота (0°, 90°, 180°)

001 in ax, D1 {проверка начального положения манипулятора}

002 cmp ax, 0

003 je m2

004 mov ax, 1

005 call gor

006 m2: in ax, D2

007 cmp ax, 0

008 je m3

009 mov ax, 1

010 call ver

011 m3: in ax, D3

012 cmp ax, N0

013 je m4

014 mov ax, 1

015 mov bx, N0

016 call pov

017 m4: in ax, D4

018 cmp ax, 0

019 je m5

020 mov ax, 1

021 call sg

022 m5: in ax, D5 {проверка наличия заготовки}

023 cmp ax, 1

024 jne m5

025 mov ax, 0

026 call gor {выдвижение манипулятора}

027 mov ax, 0

028 call sg {заготовка в схвате}

029 mov ax, 1

030 call gor {втягивание манипулятора}

031 mov ax, 0

032 mov bx, N1

033 call pov {поворот к станку}

034 mov ax, 0

035 call ver {подъем}

036 mov ax, 0

037 call gor {выдвижение манипулятора}

038 mov ax, 1

039 call sg {заготовка в станке}

040 mov ax, 1

041 call gor {втягивание манипулятора}

042 m6: in ax, D6 {проверка на окончание обработки}

043 cmp ax, 1

044 jne m6

045 mov ax, 0

046 call gor {выдвижение манипулятора}

047 mov ax, 0

048 call sg {деталь в схвате}

049 mov ax, 1

050 call gor {втягивание манипулятора}

051 mov ax, 0

052 mov bx, N2

053 call pov {поворот к конвейеру с деталями}

054 mov ax, 0

055 call gor {выдвижение манипулятора}

056 mov ax, 1

057 call ver {опускание}

058 mov ax, 1

059 call sg {деталь на конвейере}

060 mov ax, 1

061 call gor {втягивание манипулятора}

062 mov ax, 1

063 mov bx, N0

064 call pov {поворот в начальное положение}

065 in ax, D7 {проверка на окончание технологического процесса}

066 cmp ax, 1

067 jne m5

068 RST

Подпрограммы

Подпрограмма горизонтального перемещения схвата

069 gor: out REV, ax

070 mov bx, ax

071 mov ax, 1

072 out DV1, ax

073 m7: in ax, D1

074 cmp ax, bx

075 jne m7

076 mov ax, 0

077 out DV1, ax

078 RET

Подпрограмма вертикального перемещения схвата

079 ver: out REV, ax

080 mov bx, ax

081 mov ax, 1

082 out DV2, ax

083 m8: in ax, D2

084 cmp ax, bx

085 jne m8

086 mov ax, 0

087 out DV2, ax

088 RET

Подпрограмма поворота схвата

089 pov: out REV, ax

090 mov ax, 1

091 out DV3, ax

092 m9: in ax, D3

093 cmp ax, bx

094 jne m9

095 mov ax, 0

096 out DV3, ax

097 RET

Подпрограмма сжатия-расжатия губок схвата

098 sg: out REV, ax

099 mov bx, ax

0100 mov ax, 1

0101 out DV4, ax

0102 m10: in ax, D4

0103 cmp ax, bx

0104 jne m10

0105 mov ax, 0

0106 out DV4, ax

0107 RET

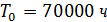

Расчет надежности

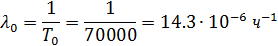

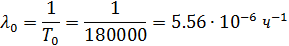

К572ПВ4 – аналогово-цифровой преобразователь со встроенным коммутатором имеет среднюю наработку на отказ  , следовательно интенсивность отказа составляет: , следовательно интенсивность отказа составляет:

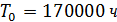

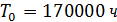

БИС управляющей памяти U831-К1883РТ1 имеет среднюю наработку на отказ  , следовательно интенсивность отказа составляет: , следовательно интенсивность отказа составляет:

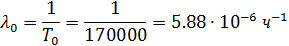

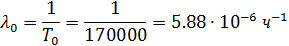

БИС арифметического устройства U830-K1883ИA0 имеет среднюю наработку на отказ  , следовательно интенсивность отказа составляет: , следовательно интенсивность отказа составляет:

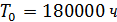

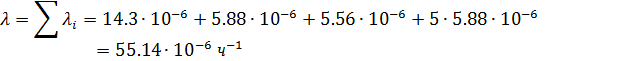

Оптронная пара имеет среднюю наработку на отказ  , следовательно интенсивность отказа составляет: , следовательно интенсивность отказа составляет:

Интенсивность отказа всей системы:

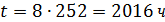

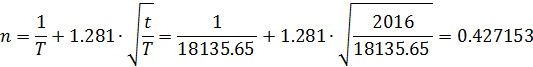

Вероятность безотказной работы системы (рабочий день – 8 часов, рабочих дней в году – 252) за год:

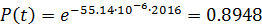

Средняя наработка на отказ:

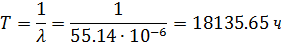

Количество отказов за год:

Список используемой литературы

1) Козырев Ю.Г. "Промышленные роботы": справочник – М.: Машиностроение. 1983. г.

2) Шахнов В.А. "Микропроцессоры и микропроцессорные комплекты": - М: Радио и Связь, 1988 г.

3) Хвощ С.Т. "Справочник по микропроцессорам: справочник – М.: Радио и связь, 1989 г.

4) Федорков Б.Г. "Микросхемы ЦАП и АЦП: функционирование, параметры, применение": - М: Энергоатомиздат, 1990 г.

|