Полтавський Військовий Інститут Зв’язку

Кафедра схемотехніки радіоелектронних систем

ОБЧИСЛЮВАЛЬНА ТЕХНІКА ТА МІКРОПРОЦЕСОРИ

напрям підготовки 0924 «Телекомунікації»

Багаторозрядні комбінаційні суматори та АЛП.

Полтава – 2006

Навчальна література.

1. Тиртишніков О.І., Корж Ю.М. Обчислювальна техніка та мікропроцесори. Частина 2. Цифрові автомати: Навчальний посібник. – Полтава: ПВІЗ, 2006, с. 80 -- 85.

2.Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника (Полный курс). – М.: Горячая линия – Телеком, 2002, с. 608 – 626.

1.

Багаторозрядні комбінаційні суматори

Принцип додавання багаторозрядних двійкових чисел полягає у тому, що у кожному з розрядів виконуються однотипні дії: визначається цифра суми шляхом додавання по модулю 2 цифр доданків і переносу з попереднього розряду і формується перенос, який надходить до наступного розряду. Ці дії реалізуються двійковим однорозрядним суматором. Така однотипність дій при додаванні різних розрядів багаторозрядних доданків дозволяє реалізувати багаторозрядні суматори як у послідовному вигляді – за рахунок послідовного виконання додавання розрядів за допомогою одного однорозрядного суматора, так і у паралельному – за допомогою схеми, що вміщує кілька однотипних фрагментів (за числом розрядів доданків), кожен з яких має свій однорозрядний суматор.

Паралельний комбінаційний суматор.

Паралельний багаторозрядний суматор складається з такої кількості однорозрядних суматорів, яка дорівнює кількості розрядів чисел, які додаються.

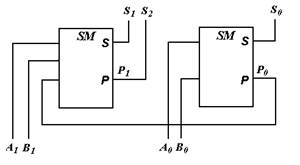

Усі розряди доданків повинні одночасно надходити до пристрою додавання. Сигнал переносу передається від розряду до розряду послідовно, утворюючи на виході значення старшого розряду суми. Схема паралельного дворозрядного комбінаційного суматора з послідовним переносом показана на рис. 1.

Рис. 1. Дворозрядний комбінаційний паралельний суматор з послідовним переносом.

Недоліком суматору з послідовним переносом є те, що отримання результату у старшому розряді суматора можливе тільки після завершення розповсюдження переносу по усіх розрядах, що знижує швидкодію пристрою. Тому інколи у схемах паралельних суматорів організують паралельний перенос. Для цього у кожному однорозрядному двійковому суматорі додатково формується сигнал розповсюдження переносу. Ідея прискорення переносу полягає у тому, що при Аi = Bi

=1у i

-му розряді буде мати місце перенос до наступного розряду, незалежно від наявності переносу із попереднього розряду. Таким чином у цьому випадку можна передавати сигнал переносу для обчислення старших розрядів, не чекаючи закінчення формування переносу із молодших розрядів. Для реалізації прискореного переносу схему паралельного суматора треба дещо ускладнити додатковими логічними елементами.

Реклама

Послідовний багаторозрядний суматор.

Послідовний багаторозрядний суматор складається з одного однорозрядного суматора та елемента затримки – наприклад, D

-тригера, що здійснює затримку сигналу переносу на один робочий такт – до надходження до входів суматору наступних старших розрядів доданків. Схема такого суматора показана на рис. 2.

Регістри зсуву в схемі призначені для передавання до входів суматора розрядів доданків у послідовному коді, починаючи з молодшого розряду, та приймання обчислених суматором розрядів суми.

Рис.2. Послідовний багаторозрядний комбінаційний суматор.

З першим тактовим синхроімпульсом на входи суматору надходять із регістрів 1 і 2 цифри молодшого розряду доданків Аi

і Bi

, а до входу переносу подається із D

-тригера логічний 0. Додаючи подані до входу цифри, однорозрядний суматор формує молодший розряд суми, який надходить до входу регістру зсуву 3 і перенос, який надходить до D

-тригера. Другий тактовий імпульс реалізує в усіх регістрах зсув чисел, що зберігаються, на один розряд праворуч; при цьому на входи однорозрядного суматору надходять цифри наступних старших розрядів доданків, і цифра переносу із D

-тригера. В подальшому робочі цикли повторяються до тих пір, поки не будуть підсумовані усі розряди доданків.

Явна перевага суматору послідовної дії полягає у малих апаратних витратах на його побудову. Але, такий суматор, у порівнянні з більш складним паралельним, має меншу швидкодію.

2.Пристрій віднімання двійкових чисел.

Комбінаційний суматор у сукупності з деякими допоміжними вузлами й елементами може бути використаний не тільки для додавання, але також для віднімання і множення двійкових чисел із знаком. Зокрема, для виконання віднімання у додаткових кодах за допомогою суматора, до від'ємника необхідно застосувати операцію доповнення, що відповідає зміні знака операнда на протилежний. Для цього в схемі пристрої додавання і віднімання варто передбачити комбінаційний пристрій, що виконує при необхідності доповнення від'ємника (інверсію всіх розрядів вихідного коду, включаючи знаковий, і додавання одиниці до молодшого розряду).

Реклама

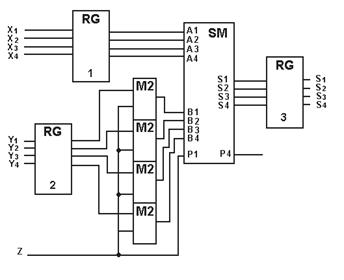

Схема чотирирозрядного пристрою додавання і віднімання двійкових чисел у додаткових кодах подана на рис. 3.

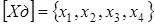

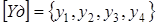

Тут  – додатковий код операнда x; – додатковий код операнда x;  – додатковий код операнда y, – додатковий код операнда y,  – додатковий код результату. – додатковий код результату.

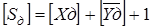

Суматор SM виконує операцію:

. .

Рис.3. Схема чотирирозрядного пристрою додавання і віднімання двійкових чисел

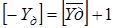

Якщо сигнал керування Z = P1 = 0, то коди операндів подаються на входи суматору без зміни, і відбувається додавання

. .

Якщо сигнал керування Z = P1 = 1, то відбувається інвертування значень усіх розрядів коду  і по каналу переносу P1 у молодший розряд додається одиниця. і по каналу переносу P1 у молодший розряд додається одиниця.

. .

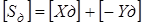

Враховуючи те, що

, ,

остаточно отримуємо:

, ,

що рівнозначно виконанню операції віднімання.

Розглянемо виконання операції віднімання на прикладі -5-(-3) = -2:

_X= - 0,101

Y= - 0,011

S= - 0,010

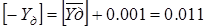

На вхід пристрою операнди надходять у додаткових кодах

; ;  . .

Після інвертування коду  і додавання одиниці до молодшого розряду одержимо: і додавання одиниці до молодшого розряду одержимо:

. .

Додатковий код різниці  знайдемо як суму знайдемо як суму  і і  : :

1.011

+0.011

1.110

Отриманий код дійсно є додатковим кодом результату (-0,0102

).

3.Основні поняття про АЛП.

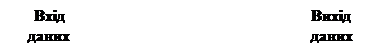

Сутність обробки інформації у цифровій формі полягає у виконанні заданої послідовності найпростіших арифметичних і логічних операцій над числами. У цифровій апаратурі основним пристроєм, у якому безпосередньо виконується обробка, є процесорний пристрій. Процесорний пристрій (як і будь-який інший складний цифровий пристрій) синтезується у вигляді поєднання двох пристроїв: операційного (арифметико-логічного) і керуючого. Структура процесорного пристрою показана на рис. 4.

Арифметико-логічний пристрій (АЛП)

призначений для виконання арифметичних і логічних операцій над числами (словами), що надходять до нього, за сигналами з пристрою керування. Основні операції, що виконує АЛП – це додавання та множення.

Пристрій керування

призначений для організації процесу обчислень. Він координує дії АЛП, генеруючі у визначеній часовій послідовності керуючі сигнали, під дією яких у вузлах АЛП виконуються необхідні операції.

Формування керуючих сигналів y1

,…,yn

(див. рис. 4) для виконання визначених мікрокоманд може залежати від стана вузлів АЛП, обумовленого сигналами x1

,…,xn

,

які передаються по відповідних колах з виходів АЛП на входи керуючого пристрою. Керуючі сигнали y1

,…,yn

можуть залежати також від зовнішніх сигналів x+1

,…,xL

.…

Результати обробки, виконані у АЛП, знімають з його виходів z1

,…,zm

...

АЛП будують на основі багаторозрядного двійкового суматору, що виконує арифметичні операції, і регістрів для зберігання операндів (даних, що беруть участь в операціях) і результатів виконання арифметичних операцій. У якості додаткових елементів АЛП містить у собі канали (шини) для передавання інформації, мультиплексори для комутації каналів, шифратори і дешифратори, лічильники, а також логічні елементи різних типів для виконання необхідних логічних операцій. Двійковий суматор у сукупності з деякими додатковими логічними елементами часто називають арифметико-логічним колом або операційним пристроєм.

АЛК, за принципом побудови, є комбінаційним пристроєм, тому що воно не має в своєму складі власних запам’ятовуючих пристроїв.

Рис.4. Схема процесорного пристрою.

Спрощена блок-схема АЛП подана на рис. 5.

Рис. 5. Спрощена схема АЛП.

Всі дані в арифметико-логічне коло і накопичувальний регістр (акумулятор) надсилаються через регістр даних. Накопичувальний регістр має розмір, що відповідає довжині машинного слова. Для того, щоб скласти два двійкових числа, одне число запам'ятовується у накопичувальному регістрі, а інше - запам'ятовується у регістрі даних. Після додавання сума двох чисел надходить у накопичувальний регістр, замінюючи вихідне двійкове число - операнд.

Процес функціонування АЛП розпадається на певну послідовність елементарних дій у його вузлах. Перелік таких елементарних дій містить у собі:

1) встановлення регістру в деякий стан;

2) інвертування вмісту розрядів регістру;

3) пересилку вмісту одного вузла в інший вузол (наприклад, пересилку числа з регістра в регістр);

4) зсув вмісту вузла (регістра) ліворуч або праворуч;

5) рахування, при якому число у лічильнику збільшується або зменшується на одиницю;

6) додавання;

7) перевірка на рівність вмісту регістра деякому числу (у разі виконання умов рівності результатом є логічна одиниця, у випадку невиконання - логічний нуль).

8) деякі логічні дії (порозрядна диз'юнкція, кон’юнкция і т.д.).

Кожна елементарна дія, виконувана у одному із вузлів АЛП протягом одного тактового періоду, називається мікрокомандою, а весь набір мікрокоманд, призначений для розв'язання визначеної задачі, - мікропрограмою.

Таким чином, якщо в АЛП передбачається можливість виконання n

різних мікрооперацій, то з пристрою керування виходять n

керуючих кіл, кожне з яких відповідає визначеній мікрооперації. І якщо в АЛП необхідно виконати деяку мікрооперацію, то досить із керуючого пристрою по певному керуючому колу подати в АЛП сигнал (наприклад, рівень логічної 1). Внаслідок того, що керуючий пристрій визначає мікропрограму, тобто які і у якій часовій послідовності повинні виконуватися мікрооперації, він одержав назву мікропрограмний автомат.

Існує два принципово різних підходи до проектування мікропрограмного автомату (керуючого пристрою): використання принципу схемної логіки або принципу програмованої логіки. Іноді ці принципи називають апаратною або програмною реалізацією цифрового автомату.

У першому випадку, тобто при використанні принципу схемної логіки, у процесі проектування підбирається деякий набір цифрових мікросхем (частіше за все малого і середнього ступеню інтеграції) і визначається така схема з'єднання їх виводів, котра забезпечує необхідне функціонування. Пристрої, побудовані за таким принципом, здатні забезпечувати найвищу швидкодію при заданому типі технології елементів, однак такі пристрої завжди виходять вузькоспеціалізованими.

Використання принципу програмованої логіки припускає побудову деякого універсального пристрою на одній або на кількох мікросхемах великого ступеню інтеграції (ВІС). Необхідний алгоритм функціонування пристрою тут забезпечується розміщенням у його пам'яті деякої певної програми (або мікропрограми).

Якщо у пристрої, побудованому за принципом схемної логіки, усяка зміна або розширення набору виконуваних функцій тягне за собою його демонтаж і монтаж за новою схемою, то при використанні програмованої логіки така зміна досягається лише заміною програми, що зберігається у пам'яті, на нову. Тому в останні два десятиліття реалізація складних цифрових автоматів з програмованою логікою мала переважне поширення.

В И С Н О В О К

Комбінаційний суматор у сукупності з деякими допоміжними вузлами й елементами може бути використаний не тільки для додавання, але й також для віднімання і множення двійкових чисел із знаком. Тому він є основою для побудови операційних пристроїв і універсальних арифметико-логічних пристроїв.

Арифметико-логічний пристрій (АЛП) призначений для виконання арифметичних і логічних операцій над числами (словами), що надходять до нього, за сигналами з пристрою керування. Процес функціонування АЛП являє собою визначену послідовність елементарних дій у його вузлах. Кожна елементарна дія, яка виконується в одному з вузлів АЛП протягом одного тактового періоду, називається мікрокомандою, а весь набір мікрокоманд, призначений для розв'язання визначеної задачі - мікропрограмою.

Пристрій керування призначений для організації процесу обчислень. Він координує роботу АЛП, генеруючі у визначеній часовій послідовності керуючі сигнали, під дією яких у вузлах АЛП виконуються необхідні операції. Пристрій керування також називають мікропрограмним автоматом.

Сукупність операційного пристрою і пристрою керування називають процесорним пристроєм або просто процесором. Процесор, у сукупності з запам'ятовуючим пристроєм і пристроями введення-виведення інформації утворюють структуру, яка одержала назву універсальної цифрової обчислювальної машини з програмним керуванням або універсального програмного автомату.

Існує два принципово різних підходи до проектування складних цифрових автоматів: використання принципу схемної логіки або принципу програмованої логіки. Іноді ці принципи називають апаратною або програмною реалізацією цифрового автомата.

|